图像传感器是相机的重要组成部分, 目前常用的图像传感器主要分为CMOS图像传感器(CIS)和CCD图像传感器。CMOS图像传感器由于具有低功耗和高帧率等特点, 获得了大量的关注。在航空测绘、天文观测等应用领域需要高分辨率的CMOS图像传感器来获取更加清晰的物体细节[1-4]。在二维CMOS图像传感器中, 高分辨率意味着较大的像素阵列和较大的芯片面积。为了使像素阵列中的行控制总线具有较高的信号建立速度, 一般会在阵列的两侧各设计一个行逻辑控制及驱动电路[5-7]。

拼接技术的长足发展[8]为超大阵列CIS的研究、设计和实现提供了制造保障。在超大阵列的CIS中, 由于像素阵列的横向宽度较宽, 位于芯片左下角的时序控制模块向右侧的行驱动模块传输信号时就需要经过一条长距离传输线, 长距离传输线引入的较大寄生电阻与寄生电容导致信号在传输过程中产生了较高的延迟, 而时序控制模块到左侧行驱动模块的传输距离比较短, 短距离传输产生的延迟也比较小, 这样就导致了左右两侧的行驱动模块接收到信号的延迟时间有较大的悬殊, 产生了不一致性,进而导致行驱动模块输出的信号也具有不一致性, 这对大阵列CMOS图像传感器的帧率、驱动信号的对称性产生了较大的影响。

在数字IC后端的设计中, 通常采用类似时钟树的技术来解决这一不一致性问题[9-10]。由于超大阵列CMOS图像传感器芯片的版图面积已经超出掩膜版面积, 所以为了最大限度降低光刻板的使用率, 必须采用拼接工艺, 同时可以保证光电处理电路的一致性。高效率的拼接工艺对电路设计和版图设计提出了很高的复用性要求, 这使得传统的时钟树设计方法将无法使用。采用拼接工艺的超大阵列CMOS图像传感器如果采用类似时钟树的技术来保证双侧行驱动信号的一致性, 就会限制面阵的规模增加, 同时会大幅度增加设计的复杂度和流片的成本。因此文献[11]中不采用时钟树技术, 而是通过延迟锁相环设计提高了两侧行驱动信号的一致性, 但是一个锁相环只能用于一个行逻辑信号, 当同时有多个行逻辑信号需要同步时, 就需要多个延迟锁相环同时工作, 这样就会导致更多的面积和功耗损耗。超大阵列CIS的帧率一般只有区区几帧[7, 12-13], 这与像素阵列的行列总线的超大寄生密不可分。行列总线的寄生效应导致信号建立速度过慢问题限制了行读出速度, 进而导致帧率较低[14]。像素阵列双侧的一致性驱动对缩小行时间、提高帧率具有一定的帮助。

针对以上问题, 本文基于延迟检测与精确补偿技术提出一种自适应校正方法, 可应用于拼接工艺技术, 具有较高的可靠性并能保证双侧行驱动信号具有较高的一致性。

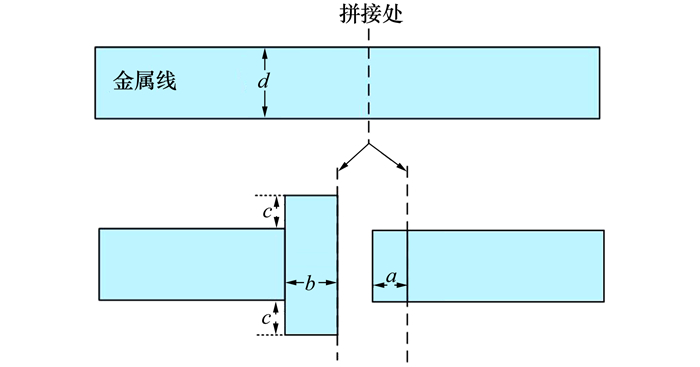

1 拼接型CIS驱动电路的难点分析 1.1 拼接工艺在设计中的应用及制约包括除像素阵列外的其他电路,12 288×12 288像素阵列的CIS,其尺寸(77 mm×84 mm)明显大于典型掩膜版尺寸(26 mm×33 mm)。目前, 生产这种芯片唯一可行的方法是利用拼接技术, 该技术允许芯片的不同部分在晶圆上以非常高的精度重复。在拼接工艺中, 只要满足拼接规则,有源区、阱、多晶、金属线都可以拼接。图 1所示为金属线在工艺中的拼接方法, d为线宽, b和c延伸出一个锤头区域, 可确保在拼接时具有一定的容错范围, 延伸出的金属线a在拼接时和锤头区域重叠可提高拼接成功率。在版图设计时, 需要设计拼接标识层, 用以标记出需要拼接的层。

|

| 图 1 金属线的拼接示意 |

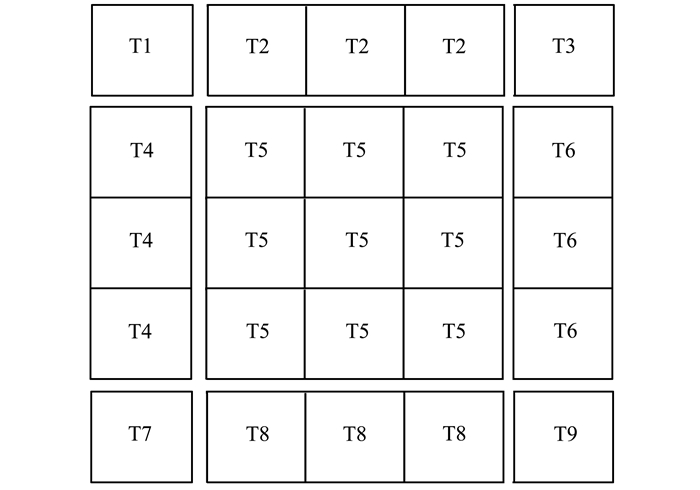

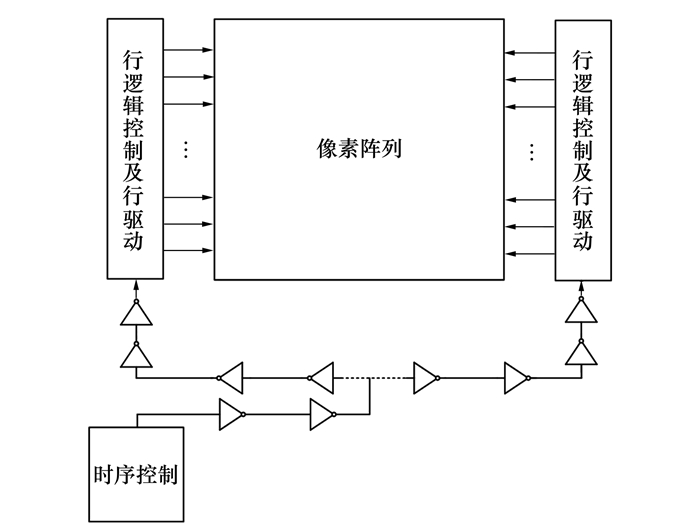

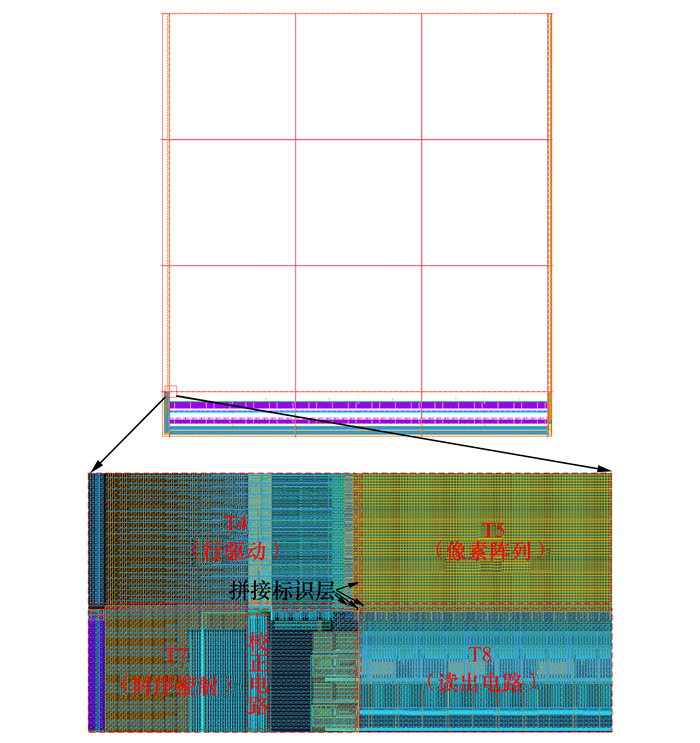

CIS电路具有较高的重复性, 是拼接应用的天然场所。重复的像素阵列是中心部分, 读出电路和引脚构成外围部分。12 288×12 288的CIS是由3×3个像素阵列在一块晶圆上拼接而成。CIS整体版图拼接方式如图 2所示, 其中T2为4 096列的尾电流源, T1为DAC模块, T3为填充的电源滤波电容, T4和T6分别为左右两侧的4 096行的行驱动模块, T5为4 096×4 096的像素阵列, T7为时序产生模块, T8为4 096列的读出电路, T9为稳压电源及基准产生模块。由于3个T8模块是完全相同的, 只需要光刻制造一个T8的掩膜版, 然后利用拼接工艺对该掩膜版进行复用, 这样不仅可以保证读出电路的一致性, 还可以节省制造成本。但是类似于图 3所示的时钟树技术在拼接型的CIS中就不适用了, 因为采用该技术需要制造3个不同的T8掩膜版, 降低了读出电路的一致性, 提高了流片成本。

|

| 图 2 1.5亿规模CIS模块版图拼接示意 |

|

| 图 3 时钟树技术示意 |

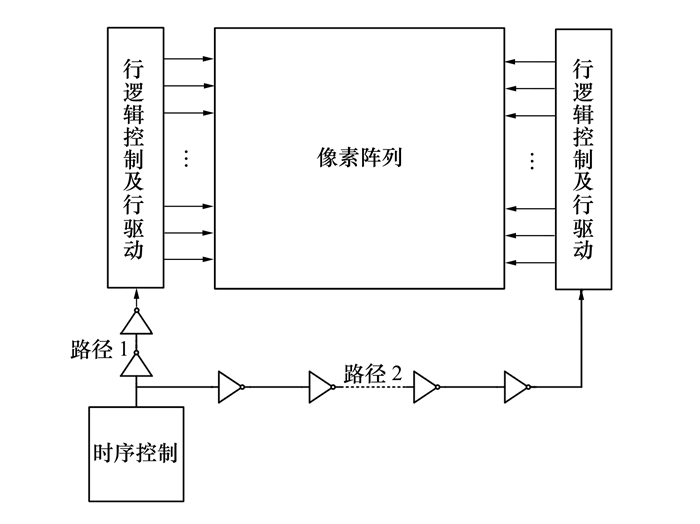

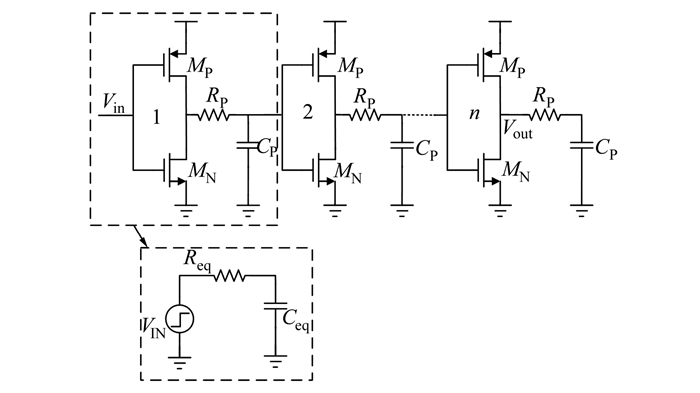

如图 4所示, 时序控制模块发出的信号经过一条缓冲链到达行驱动模块, 并且会产生一个延迟时间Td。缓冲链由一定数量的缓冲器串联而成, 其寄生模型与延迟等效模型[15]如图 5所示。

|

| 图 4 双侧驱动时序控制信号传输示意 |

|

| 图 5 缓冲链的寄生模型与延迟等效模型 |

延迟等效模型中等效电阻

|

(1) |

式中:RVDD为电源走线的寄生电阻;RP为金属线寄生电阻

|

(2) |

MOS管的导通电阻为

|

(3) |

|

(4) |

式中:L和W分别为金属走线的长度(缓冲器之间的间距)和宽度;IDSAT为MOS管工作在线性区的导通电流;λ为沟道长度调制系数。

等效电容为

|

(5) |

式中:CP为金属走线的寄生电容;Ron为MOS管的导通电阻(假设PMOS与NMOS管的导通电阻相同);CGGN和CGGP分别为NMOS管和PMOS管的栅极对地等效电容(漏极到衬底的寄生电容较小, 此处忽略了该寄生电容)。

用一阶RC电路的延迟来模拟反相器的延迟, 则由n级缓冲器构成缓冲链的延迟时间为

|

(6) |

在数字后端的设计中, 缓冲器的尺寸和电源电压VDD都是固定的, 因此延迟时间Td只与线上的寄生和电源的负载能力相关。此处电源负载能力指的不仅仅是外接的稳压电压负载能力, 还包括版图中由于电源的长走线所引入的寄生电阻, 该寄生电阻限制了对寄生电容的充放电能力, 进而导致延迟增加。

如图 4所示, 时序控制模块发出的逻辑控制信号经过较短的路径1并历经Td1时间到达像素阵列的左侧的行驱动模块, 经过较长的路径2并历经Td2时间到达像素阵列右侧的行驱动模块, 且延迟时间Td2大于延迟时间Td1。Td1和Td2之间的延迟差值表示为

|

(7) |

ΔT直接导致了两侧行驱动模块输出的不一致性, 这将降低像素阵列中行总线信号的建立速度, 最严重的情况将导致左右行驱动模块的短路。

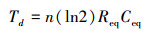

1.3 亿级像素规模下的非一致性实验分析在12 288×12 288像素规模的CIS中,单个像素的宽度为5.5 μm,时序控制模块的输出端到达右侧行驱动的输入端的距离大约为73 mm, 在每一毫米间隔插入一个缓冲器的设计前提下, 当电源的供电能力较为理想时, 线宽与延迟时间差(ΔT)的关系如图 6所示。后仿真实验数据显示, 线宽越宽, 延迟时间差越高。而随着线宽增加,寄生电阻减小,寄生电容增加。可见,延迟时间差对于寄生电容较为敏感,寄生电阻的大小几乎不会影响延迟时间。

|

| 图 6 线宽与延迟差的关系 |

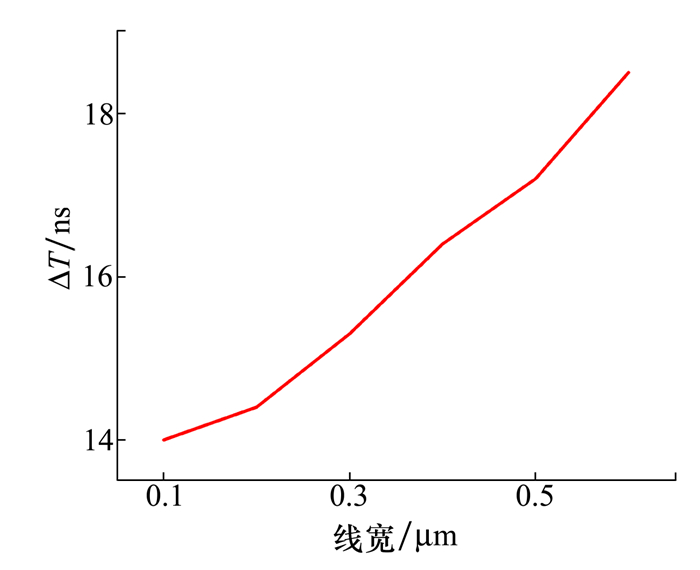

受制造工艺水平的限制, 最小线宽为0.1 μm, 在缓冲器间隔为1 mm的情况下, 延迟时间受到电源驱动能力的限制。后仿真实验结果如图 7所示, 当电源的内阻(Rs)越高时, 左右两侧的延迟时间差随之线性增加。当电源内阻较大时, 减慢了对寄生电容的充放电速度, 致使延迟时间增加。

|

| 图 7 电源内阻与延迟差的关系 |

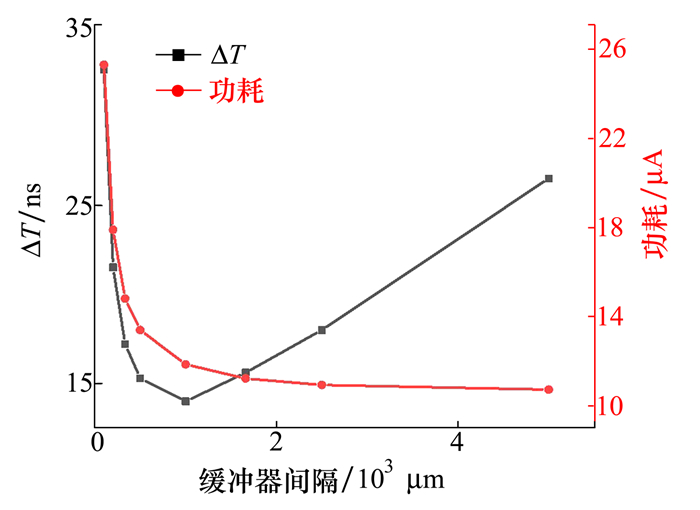

在电源较为理想的情况下, 采用0.1 μm的最小线宽, 通过后仿真实验研究了缓冲器间隔对延迟时间差的影响, 实验结果如图 8所示。随着缓冲器间隔增加, 延迟时间差先减小后增加, 在间隔为1 mm左右时, 延迟时间差最小。功耗随着缓冲器间隔的增加而减小。

|

| 图 8 缓冲器的间隔对延迟时间差的影响 |

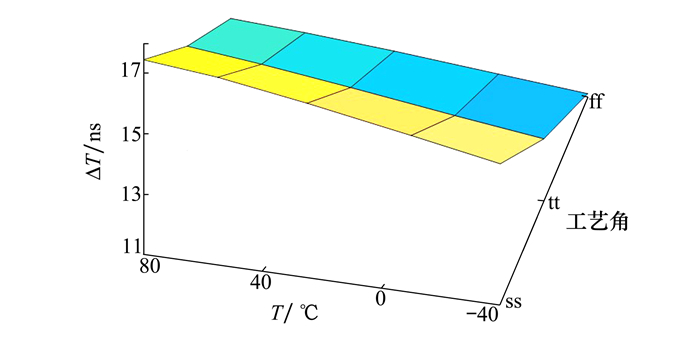

在电源较为理想的情况下, 采用0.1 μm的最小线宽, 缓冲器间隔为1 mm, 对缓冲链在不同温度及工艺角下进行了后仿真实验, 实验结果如图 9所示。结果显示, 无论在哪个工艺角下, 延迟时间差都会随着温度的增加而增加。温度一定的情况下, ss工艺角对应延迟差最大为17.5 ns, ff工艺角对应的延迟差最小为11.1 ns。

|

| 图 9 延迟差在不同温度及工艺角下的表现 |

由以上的实验结果可知, 在缓冲器尺寸固定的情况下, 延迟时间与金属走线线宽、电源驱动能力、缓冲器间距、环境温度及工艺角有很大关系。从电路设计角度考虑, 通过降低走线宽度、提高电源的驱动能力、保持合适的缓冲器间距有利于降低缓冲链的延迟时间。

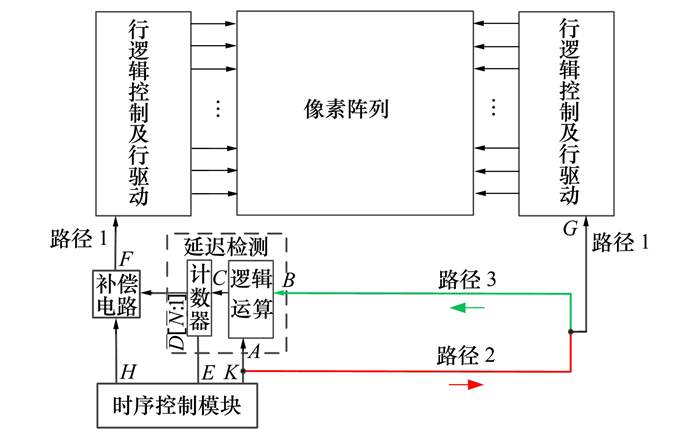

2 基于延迟检测与精确补偿的自校准方法大阵列CIS双侧行驱动信号自适应校正技术方案如图 10所示。电路从功能上主要区分为延迟检测电路和补偿电路两部分。延迟检测电路用于检测路径2和路径3的总延迟时间并将总延迟时间转化为计数器的计数值。计数器的一半计数值配置到补偿电路中, 使补偿电路产生的延迟时间与路径2产生的延迟时间相等。因此, 在版图设计中, 需要保证路径2与3的寄生环境、插入缓冲器的数量、线宽是相同的, 即保证二者的延迟时间相同。延迟检测完成后, 当时序控制模块发出逻辑信号时, 逻辑信号经过路径2到达右侧行驱动的输入端G, 经过补偿电路到达左侧行驱动的输入端F。此时, 两侧行驱动的一致性表现就取决于路径2延迟时间和补偿电路延迟时间的匹配程度, 而补偿电路的延迟时间受延迟检测电路的精度制约。

|

| 图 10 延迟检测与补偿技术结构 |

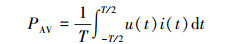

理想情况下, 路径2的延迟时间可以表示为

|

(8) |

式中:TDTD为延迟检测电路检测到的延迟时间(delay time detection, DTD);Tclk为时钟周期;TDC为补偿电路的延迟时间(delay circuit, DC)。TDTD的值由计数器产生, 计数器误差始终在一个时钟周期以内。

实际上, 路径2和路径3中的缓冲链在版图上不能完全匹配, 导致2条路径的传输延迟不同, 也会导致校正后的非一致性问题。

考虑到由于路径2和3不匹配造成的误差, 则路径2和路径3的平均延迟时间可以表示为

|

(9) |

式中:TE为路径2和路径3由于不匹配所造成的延迟差。为了使路径2和3的缓冲链具有较高的匹配度, 在设计中, 采用了如图 11所示的版图布局, 后仿真验证结果显示, 这2条路径的延迟差小于100 ps, 不会使校正结果产生较大的误差。

|

| 图 11 具有高匹配性的缓冲链布局 |

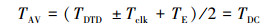

延迟时间检测功能的工作时序如图 12所示, 在初始时刻A~H及K端的信号均为低电平。在延迟时间检测阶段F和H始终保持为低电平。

|

| 图 12 延迟检测工作时序 |

首先, 在t1时刻, 时序控制模块从E端输出高电平, 使计数器使能控制打开。同时, 时序控制模块从K输出端发出一个脉冲信号并首先到达逻辑运算电路的A输入端, 由于K端到A端的距离很近, 所以K端信号与A端信号是同相位。此时, 逻辑运算电路检测到A端信号的上升沿, 便从输出端C输出高电平, 并控制计数器开始计数。

接着, 当时序控制模块从K端发出的脉冲信号沿路径2到达右侧的行驱动模块输入端G时, 脉冲信号沿路径3返回, 并在t2时刻到达逻辑运算电路的B输入端。此时, 逻辑运算检测到B端的上升沿, 便从输出端C输出低电平, 控制计数器停止计数。此时计数器输出的计数值(D[N∶0])就是路径1和2总延迟时间计数值。由于路径2和3相同, 所以计数器输出的计数值的一半(D[N∶1])就为路径2延迟时间的计数值。至此, 延迟检测完成。

最后, 计数器计数值的高位(D[N∶1])对补偿电路的延迟时间进行配置, 补偿电路将会根据配置的延迟时间产生延迟。

此后, 时序控制模块发出的信号经过补偿电路到达左侧的行驱动模块的输入端F, 经过径路2到达右侧行驱动模块的输入端G, 补偿电路的延迟时间等于路径2的延迟时间, 则F点和G点的信号就可以保持较高的一致性。

下面结合图 13的具体电路对同步过程进行具体介绍。或门(OR)、D触发器、与门(AND), 三者构成逻辑运算电路。计数器1的使能端EN由时序控制模块进行控制, 输入端IN连接与门的输出端。

|

| 图 13 自适应校正具体实现电路 |

计数器2, 7个同或门(XNOR)、7输入的与门, 三者构成延迟电路(即补偿电路)。计数器2的使能端EN由时序控制模块进行控制, 7个同或门的输入端连接计数器1的高7位D[7∶1], 高7位为路径2的延迟时间。

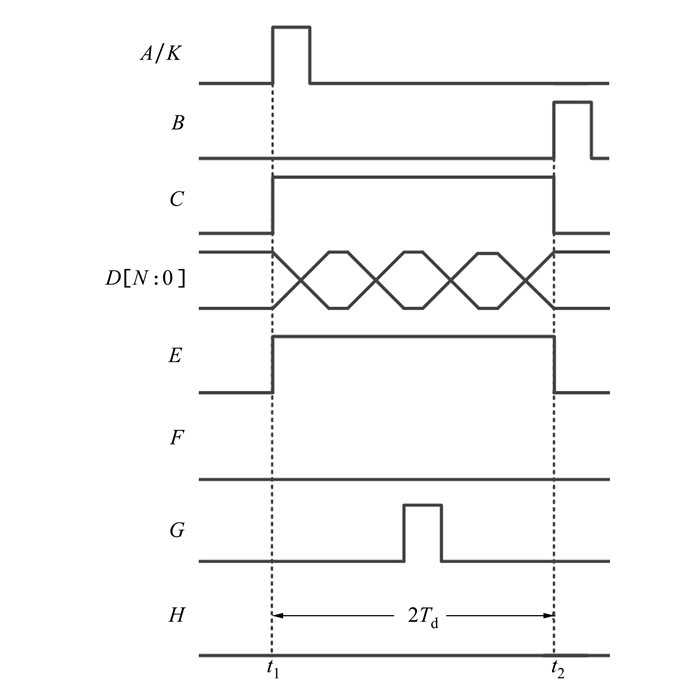

电路按照图 12时序完成延迟检测后, 将计数器1的使能端E置为低电平, 使计数器1的计数值D[7∶0]保持不变。计数器1的高7位D[7∶1]分别输入到延迟检测电路中的7个同或门的输入端, 完成对补偿电路的延迟时间配置。双侧一致性驱动的具体实现波形如图 14所示, 在初始时刻A~J的信号均为低电平。

|

| 图 14 双侧一致性驱动的具体实现波形 |

首先, 在t1时刻, 时序控制模块从K端发出时序信号并向右侧行驱动的输入端G端传输, D触发器检测到时序信号的上升沿, 使得C端输出高电平。同时, I端发出高电平信号, 计数器使能有效, 计数器2开始计数。

其次, 在t2时刻, 当计数器2的计数值与计数器1高7位的值相等时, 7输入与门输出端J输出高电平到时序控制模块。时序控制模块从H端输出时序信号并到达左侧行驱动的输入端F, 此时在t1时刻从K端发出的信号也到达了G端, 实现了F端与G端的信号同步。

最后, 或门的输入端B虽然接收到了返回时序信号的上升沿, 并使C端信号做出翻转, 但是由于计数器1的使能端信号E一直处于低电平, 所以不能改变计数器1的计数值。即, B端和C端信号在同步过程中不影响电路的逻辑。

通过上述方式, 可大幅提高双侧行驱动模块接收到信号的一致性, 则行驱动的输出也会保持较高的一致性, 可使得像素阵列同时从左右两侧获得一个相对均衡的驱动信号, 有效防止大电流贯穿。该电路可以在芯片上电之后开始进行延迟检测, 当CIS由于连续工作而发热时, 为确保一致性, 也可以在帧曝光开始前进行一次延迟检测, 以达到实时校正的工作状态。

自适应校正电路的功耗主要来源为计数器的高频计数。由于缓冲链工作频率低, 每个缓冲器的功耗低至10-2A, 每一毫米的间隔插入一个缓冲器, 1条7 mm长的缓冲链的功耗也极低。

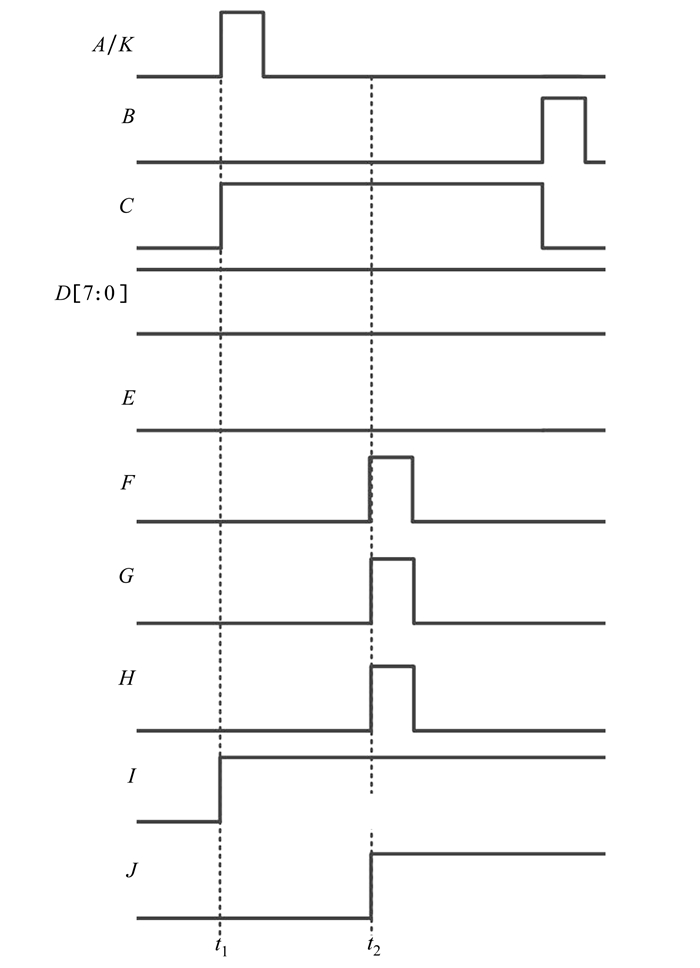

平均功耗的表达式为

|

(10) |

自适应校正电路后仿真平均功耗小于3 μW。

3 延迟检测与精确补偿技术的实验结果与分析本设计基于55 nm CMOS图像传感器专用工艺, 主时钟为500 MHz的固定工作频率时, 在不同线宽和不同电源带载能力的情况下, 对提出的非一致性解决方法进行了实验验证。图 15为12 288×12 288 CIS的局部版图, 本文提出的校正电路位于T7拼接块。

|

| 图 15 整体版图及校正电路的具体位置 |

在实际的设计实现中, 芯片内部电源存在一定干扰, 尤其是在大面阵图像传感器芯片面积较大时, 电源平面的差异非常大, 所以本文在全芯片设计时其实采用的是二次电源动态管理技术, 在确定的电源电压下, 为了探究寄生效应对校正电路的影响, 本文设计了不同线宽的缓冲链, 并进行了提参后仿真。后仿真结果如图 16所示, 采用校正技术后, 在0.1到0.6 μm线宽的区间内, 两侧行驱动的时间差由14~18.5 ns缩减为0.03~1.7 ns。信号到达左右两侧的时间差ΔT小于1个时钟周期, 且线宽的变化对校正后的时间差影响较小。

|

| 图 16 校正前后线宽与延迟时间差的关系 |

在线宽为0.1 μm时, 为了验证电源内阻大小对校正结果的影响, 本文采用不同内阻的电源进行了后仿真验证。实验结果如图 17所示, 采用校正技术后, 在0~600 Ω电源内阻的区间内, 两侧行驱动的时间差由14~25.2 ns缩减为0.03~1.7 ns。信号到达左右两侧的时间差ΔT小于1个时钟周期, 且随着电源内阻变化未发生较大变化。

|

| 图 17 校正前后延迟时间差与电源内阻的关系 |

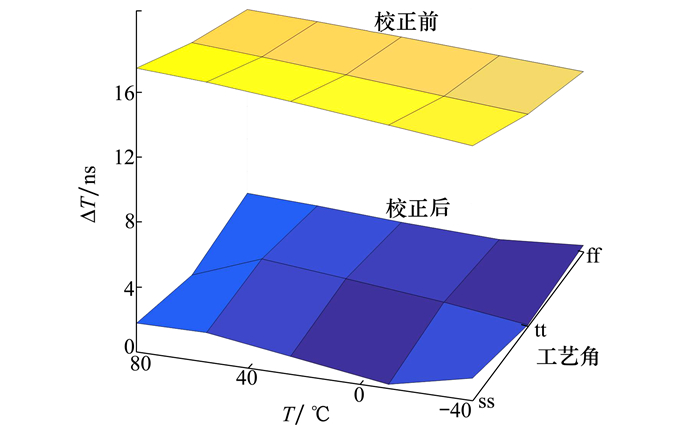

为了进一步验证校正电路的可靠性,在-40~80 ℃温度区间, 对该电路在不同工艺角下的工作状况进行了仿真实验。仿真结果如图 18所示, 校正后的延迟差稳定在0.17~1.81 ns之间, 几乎不随温度及工艺角的变化而变化。而校正前, 在该温度范围内延迟差在11.1~17.5 ns之间, 并且随着温度和工艺角的变化, 延迟差近似线呈性变化。校正后的一致性主要受限于计数器的时钟频率, 时钟频率越高, 校正后的非一致性越好, 但是需要考虑与芯片内部的频率源能力匹配。

|

| 图 18 在不同温度及工艺角下校正后的实验结果 |

通过以上在不同的线宽、电源内阻、温度及工艺角情况下的实验结果可以得出, 基于延迟检测与精确补偿的自适应校正技术在恶劣的环境下可以稳定工作, 具有较高的可靠性。本文校正后的非一致性在2 ns以内, 与文献[11]中采用的锁相环校正技术达到的小于1 ns的非一致性相比, 结果略差, 但是该方法使用的是纯数字电路具有极低的功耗, 平均功耗小于3 μW。

4 结论本文分析了拼接型的超大面阵的CMOS图像传感器在设计过程中遇到的双侧行驱动信号不一致性的问题, 并详细地分析该问题的产生的具体原因。为解决该非一致性问题, 本文在设计中采用了一种基于延迟检测与精确补偿的自适应校正技术。基于55 nm CMOS图像传感器工艺, 该技术在12 288×12 288像素阵列、整体芯片尺寸为77 mm×84 mm的CMOS图像传感器上实现了对两侧像素阵列的一致性驱动。后仿真结果表明, 在500 MHz的时钟频率下, 双侧行驱动的非一致性由17.5 ns以上减小到2 ns(一个时钟周期)以内, 一致性提高了9倍以上。确保了亿级像素规模的超大面阵图像传感器的帧频达到10帧以上。

| [1] | KIM Y, CHOI W, PARK D, et al. A 1/2.8-inch 24M pixel CMOS image sensor with 0.9 μm unit pixels separated by full-depth deep-trench isolation[C]//Proceedings of the 2018 IEEE International Solid-State Circuits Conference, 2018 |

| [2] | KIM H, PARK J, JOE I, et al. 5.6 A 1/2.65in 44M pixel CMOS image sensor with 0.7 μm pixels fabricated in advanced full-depth deep-trench isolation technology[C]//Proceedings of the 2020 IEEE International Solid-State Circuits Conference, 2020 |

| [3] | HSU T H, CHEN Y K, WU J S, et al. 5.9 A 0.8 V multimode vision sensor for motion and saliency detection with ping-pong PWM pixel[C]//Proceedings of the 2020 IEEE International Solid-State Circuits Conference, 2020 |

| [4] | SONG K, KIM D, KIM J, et al. A scalable 300-GHz multichip stitched CMOS detector array[J]. IEEE Trans on Microwave Theory and Techniques, 2022, 70(3): 1797-809. DOI:10.1109/TMTT.2021.3118305 |

| [5] | XU J, LI W, NIE K, et al. A Method to reduce the effect on image quality caused by resistance of column bus[J]. IEEE Trans on Very Large Scale Integration Systems, 2019, 27(1): 173-181. DOI:10.1109/TVLSI.2018.2870858 |

| [6] | GAO J, ZHANG D, NIE K, et al. Analysis and optimization design of the column bus parasitic effects on large-array CMOS image sensor[J]. Microelectronics Journal, 2019, 96: 104681. |

| [7] | BOGAERTS J, LAFAILLE R, BORREMANS M, et al. 6.3 105×65 mm2 391M pixel CMOS image sensor with>78 dB dynamic range for airborne mapping applications[C]//Proceedings of the 2016 IEEE International Solid-State Circuits Conference, 2016 |

| [8] | ZHU J, LIU D, ZHANG W, et al. Systematic experimental study on stitching techniques of CMOS image sensors[J]. IEICE Electronics Express, 2016, 13(15): 20160441. DOI:10.1587/elex.13.20160441 |

| [9] |

高静, 张天野, 聂凯明, 等. 超大阵列CMOS图像传感器时序控制驱动电路设计[J]. 天津大学学报, 2021, 54(1): 75-81.

GAO Jing, ZHANG Tianye, NIE Kaiming, et al. Design of timing driven circuit for ultra large array CMOS image sensor[J]. Journal of Tianjin University, 2021, 54(1): 75-81. (in Chinese) |

| [10] | SONG Y, LI P, LIU Z, et al. Buffer reduction for congestion control during timing optimization[C]//Proceedings of the 2022 IEEE 2nd International Conference on Power, Electronics and Computer Applications, 2022 |

| [11] | GUO Z J, YU N M, WU L S. A synchronous driving approach based on adaptive delay phase-locked loop for stitching CMOS image sensor[J]. IEICE Electronics Express, 2020, 17(3): 20190642. DOI:10.1587/elex.16.20190642 |

| [12] | TOTSUKA H, TSUBOI T, MUTO T, et al. 6.4 An APS-H-size 250 Mpixel CMOS image sensor using column single-slope ADCs with dual-gain amplifiers[C]//Proceedings of the 2016 IEEE International Solid-State Circuits Conference, 2016 |

| [13] | JUN J, SEO H, KWON H, et al. A 0.7 μm-pitch 108M pixel nonacell-based CMOS image sensor with decision-feedback technique[C]//Proceedings of the 2022 IEEE International Symposium on Circuits and Systems, 2022 |

| [14] | GUO Z J, CHENG X Q, XU R M, et al. A 1G pixel 10FPS CMOS image sensor using pixel array high-speed readout technology[J]. Integration-The VLSI Journal, 2023, 89: 114-122. DOI:10.1016/j.vlsi.2022.12.002 |

| [15] | OGATA M, OKABE Y, NISHI T. Simple RC models of distributed RC lines in consideration with the delay time[C]//Proceedings of the 2004 IEEE International Symposium on Circuits and Systems, 2004 |