2. 西安电子科技大学 微电子学院, 陕西 西安 710065

随着微处理器母板、智能集线器、路由器、光通信链路及芯片与芯片间等通信链路速度的快速提升,不断推动着片外数据传输速率向高达每秒千兆位以上的速度发展[1-4]。低压差分信号LVDS发送器作为一种常见的串行数据发送电路,在高速应用场合中得到了广泛应用。目前,空间遥感测绘、对地观测等宇航应用都需要超大面阵规模CMOS图像传感器作为支撑,有效像元个数达上亿,如此巨大的像素阵列都需要通过列并行高速ADC读出电路将模拟信号转换成数字码输出,因此对读出链路后级的高速数据接口提出了更高的要求, 本文工作正是基于这个需求背景展开。

常见的高速串行数据接口包含多种,而低压差分信号传输数据接口以其高速抗共模干扰及EMI等特点,在各种传感器接口电路中得到广泛应用。典型LVDS驱动器以桥型开关电流源(bridge switch current source,BSCS)拓扑作为驱动器核心结构,理论上在无损传输时最高速率为655 Mb/s[5-6],由于传输信道的不理想性,有损传输会导致传输速率下降,实际的传输速率在400 Mb/s左右。2005年,Chen等[7]提出了双电流源拓扑(double current source,DCS)和可切换电流源(switchable current source,SCS)LVDS驱动器拓扑结构,在0.35 μm工艺下速度达到1.4 Gb/s和1.2 Gb/s,但是驱动负载能力较小只有6 pF,而功耗高达23 mW和12.8 mW。2007年,Yeong等[8]利用0.13 μm工艺设计实现了速率为1.2 Gb/s的LVDS驱动器,负载为6 pF时功耗为67.5 mW;2009年,Wang等[9]利用0.18 μm工艺设计实现了2 Gb/s的LVDS驱动器,功耗为13.2 mW;2010年,Wonki等[3]利用0.18 μm工艺设计实现了带预加重功能的LVDS驱动器,速率达到3.125 Gb/s,容性负载为5 pF下功耗为48 mW。2011年,Yang等[10]利用0.13 μm工艺设计实现了速率为1.2 Gb/s的LVDS驱动器,驱动6 pF负载时功耗为16.5 mW;2012年,Ge[11]在0.11 μm工艺下设计实现了速率为400 Mb/s的LVDS驱动器,驱动负载能力达到10 pF,但是传输速率比较低只有400 Mb/s,功耗为12 mW。2017年,Gian等[12]在28 nm工艺下设计实现了速率达1 Gb/s的LVDS驱动器,驱动负载能力小于6 pF功耗8.7 mW。

文献[2, 10-11]采用的共模反馈电路是电流镜带米勒补偿的运放结构,主要为了获得较高带宽,但是增益只有18 dB[11];文献[7]采用共源共栅结构带米勒补偿的运放结构,增益达到60 dB, 但是带宽较小,一般情况下在20~30 MHz范围内。在大容性负载(如12 pF以上寄生电容的板级测试等应用场合)高速传输过程中,LVDS驱动器电路共模反馈电压不稳定,从而导致高速信号传输质量变差,误码率上升,因此必须在增益、带宽及功耗三者之间进行设计优化,满足高速高精度低功耗的设计指标。

本文所提出的LVDS驱动器设计方案正是基于上述应用背景,在已有的LVDS驱动器设计基础上,针对常用的LVDS驱动器驱动容性负载能力弱、高速数据传输时共模反馈电压精度不高、增益和带宽不能同时兼顾以及预加重结构复杂等缺点,提出了一种基于沟道长度分割补偿方法的共模反馈电路结构,在保证增益的前提下,带宽提高到100 MHz以上。同时采用了与文献[2-3, 10]中预加重拓扑结构相比更加简单高效的预加重结构,提高了容性负载驱动能力,通过对高速传输过程中的高频分量进行幅度补偿,提高了高速信号传输的质量。本文所提出的设计方案,不但可以满足高速高精度的需求,而且在功耗方面也达到了最小。

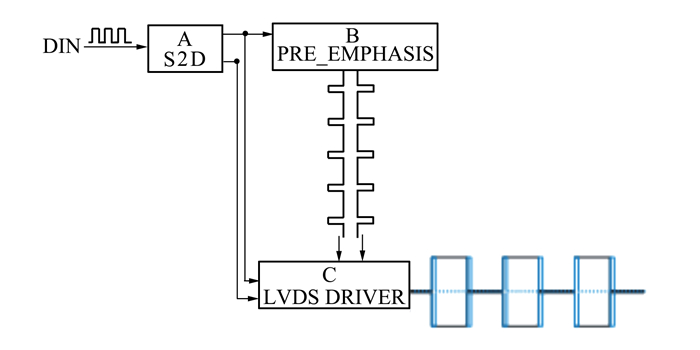

1 整体架构高速串行数据驱动器整体结构主要有2种类型:①电流模式(CML)驱动器;②电压模式(VML)驱动器。典型LVDS驱动器属于电流模式发送器,LVDS驱动器主要功能是将高速串行数据转换成低压差分信号然后进行传输,因此具有抗共模干扰和EMI的优点。图 1为带预加重功能的LVDS驱动器功能示意图。

|

| 图 1 LVDS发送器器整体结构 |

LVDS驱动器整体结构由图 1中3个模块组成,其中模块A为单端转差分电路(single to differential,S2D)、模块B为预加重功能电路(PRE_EMPHASIS)、模块C为LVDS主驱动器电路。文中提出的高速高精度低功耗LVDS驱动器晶体管级电路如图 2所示。

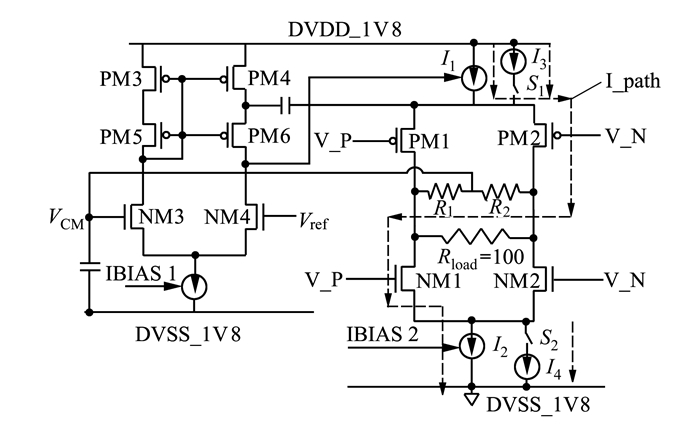

|

| 图 2 晶体管级LVDS发送器电路结构 |

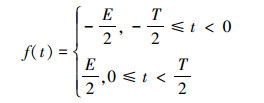

图 2中,DVDD_1V8表示1.8 V数字电源电压,DVSS_1V8表示1.8 V对应的数字地。VCM表示LVDS驱动器的共模反馈电压,Vref表示参考电压,IBIAS2表示电流漏I2的偏置电压,I1和I2分别为PMOS电流源和NMOS电流漏,I3和I4分别为预加重时的电流源和电流漏,切换开关S1和S2的控制时序由预加重逻辑电路产生。左侧电路为高增益宽带运算放大器电路,右侧电路为典型桥型开关电流源的改进结构电路,增加了预加重功能。

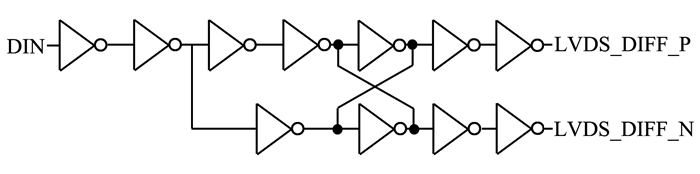

2 高速高精度低功耗驱动器电路设计 2.1 单端转差分电路单端转差分信号电路实现将高速单端数字逻辑信号转换成2路相位相差180°的差分信号。首先需要将待传输的高速数字信号经过由2个反相器组成的buffer电路缓冲后,一路经过由2个反相器组成的缓冲器电路,另一路经过一个反相器实现相位翻转180°,从而得到一路与输入信号同相另一路与输入信号反相的差分信号,接着再经过一对由反相器交叉耦合对组成的边沿对齐电路,实现差分信号边沿对齐的功能,最后再分别经过一个buffer驱动电路后得到差分信号LVDS_DIFF_P和LVDS_DIFF_N,图 3为所设计的单端转差分信号电路。

|

| 图 3 单端转差分信号逻辑电路 |

主驱动器电路采用的是典型桥型开关电流源拓扑结构设计,如图 4所示。

|

| 图 4 本文提出的LVDS发送器拓扑结构 |

图 4中左侧虚线框内为典型LVDS驱动器桥型开关电流源拓扑结构,其中PMOS管PM1和PM2、NMOS管NM1及NM2组成的4个开关实现高速信号的状态切换,上下电流源I1和I2为标准3.6 mA电流。输入信号V_P和V_N是单端转差分后的高速信号,当发送逻辑电平为1,也就是V_P为高V_N为低时,开关PM2和NM1打开,开关PM1和NM2关闭,从而形成从电流源I1(典型值为3.6 mA)流经开关PM2和负载电阻(外接100 Ω精准电阻)以及开关NM1到达电流漏I2(典型值为3.6 mA),即形成压降为正360 mV的电压信号。反之,形成压降为负360 mV的电压信号,实现发送逻辑电平0的功能。

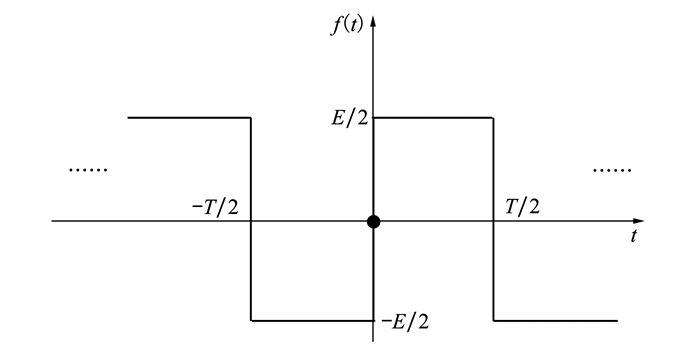

2.3 预加重功能电路设计高速数据信号传输过程中,由于传输信道的不理想性、封装寄生电容的影响以及接收端容性负载大等因素,会造成传输速率越高,信号中的高频成分衰减越厉害,也就会使得信号波形变差和失真导致误码率升高,从而限制了信号传输速率。因此,为了达到1 Gb/s以上的高速信号传输,需要设计预加重电路对损失的高频成分进行补偿,从而改善高速率传输时的信号波形以提高信号完整性,减小误码率。根据所要传输的数据信号的波形,本文以常见的方波信号为例,波形如图 5所示。

|

| 图 5 幅值为周期为T的方波信号 |

图 5所示的方信号对应的时域表达式为

|

(1) |

公式(1)所对应的傅里叶级数展开式为

|

(2) |

由公式(2)可知, 所要传输的高频方波信号的频谱由基波和众多奇次谐波分量组成, 不包含偶次谐波成分。在高速信号传输过程, 衰减最严重的是方波信号的高频分量, 包括3次谐波、5次谐波、7次谐波等高频分量, 其中谐波次数越高衰减越严重。

本文设计的预加重功能电路基本原理是通过对高次谐波分量进行幅度增强处理, 以期通过该方法实现对传输的高速信号进行高频分量补偿的目的。具体做法是利用预加重开关控制预加重电流源在高速信号电平切换的过程中对衰减严重的奇次高频谐波分量进行幅度增强, 从而得到跟原始方波信号相比失真较小的方波信号。图 4中右侧虚线框电路为预加重功能电路, 由电流源I3和电流漏I4及状态切换开关S1和S2组成, 是一种结构简单高效的预加重电路。预加重过程中幅度增强是通过开启和关闭上下电流源I3, I4来实现, 因此能够有效改善高速传输时信号的质量, 降低误码率。

3 共模反馈电路设计 3.1 共模负反馈电路LVDS驱动器共模反馈电路是通过负反馈将输出端信号的共模电压稳定在一个固定参考电压, 共模负反馈环路的带宽和增益直接决定着LVDS发送器输出共模电压精度和差分输出信号波形对称性及其匹配性。由于LVDS驱动器需要驱动低阻抗大电容负载, 大容性负载会进一步限制共模负反馈环路带宽。一般来说, 共模反馈环路带宽要比输入信号频率高4.6倍以上, 理论上才会确保系统得到及时响应并建立稳定态, 但是对于LVDS发送器而言, 传输速率高达1 Gb/s时, 设计4.6 GHz以上带宽的运算放大器是一件非常困难和不现实的, 那么如何保证在1 Gb/s以上数据传输速率时得到稳定的共模电压就是一个亟待解决的问题。

本文针对高达1 Gb/s以上的高速数据传输, 提出了一种不同于米勒补偿的间接补偿法实现对共模反馈环路的补偿, 既可以保证较高增益又可获得高带宽。下面分析当输入信号V_P为高, V_N为低时的情形(V_P为低, V_N为高时的情况与之类似), LVDS驱动器等效电路如图 6所示, 从等效电路可以看出LVDS驱动器共模反馈环路可等效为一个两级运放进行分析和设计。下面对LVDS驱动器等效的小信号电路模型进行理论推导和分析。

|

| 图 6 LVDS发送器共模反馈环路等效电路 |

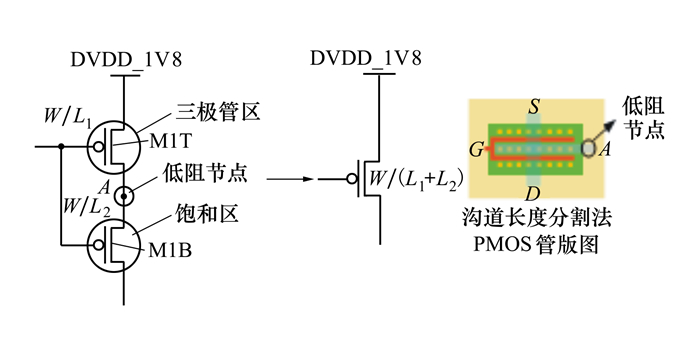

图 6中NM3、NM4及PM3~PM6为典型五管运算放大器的改进结构, 通过将电流镜负载管采用沟道长度分割方式[13]进行设计, 此设计的特点是CMOS晶体管PM3和PM4工作在深线性区而不是饱和区, 这与常见的共源共栅结构采用的间接补偿法有着本质不同。采用沟道长度分割补偿法的优点是:①不增加额外晶体管数量, 从电流镜负载输出节点1向内看进去的第一级等效输出阻抗和等效电容没有改变, 唯一需要注意的是版图设计时需要将电流镜负载管的沟道长度人为地分割开以创建一个内部低阻节点A, 从而形成从第二级输出节点2经由补偿电容Cc通过低阻节点A流向节点1的补偿电流通路, 实现对共模反馈环路的间接补偿; ②第一级输出节点1和第二级输出节点2之间由于没有补偿电容Cc的存在, 因此不会形成前向电流通路, 也就不会产生右半平面零点。采用沟道长度分割方法后的补偿电容相比米勒补偿方式可以将补偿电容的大小缩小为原来的十分之一甚至更小, 从而可以有效提升共模反馈运算放大器的带宽, 图 7为沟道长度分割补偿法原理和版图实现示意图。

沟道长度分割时需要考虑两方面因素:①在保持典型五管运放结构不变的前提下, 能够极大提高运放的单位增益带宽; ②版图设计实现时能够满足晶体管之间的匹配性。因此综合考虑上述2个因素, 文中采用将沟道长度平均分配的方式是较为合理和容易实现的。

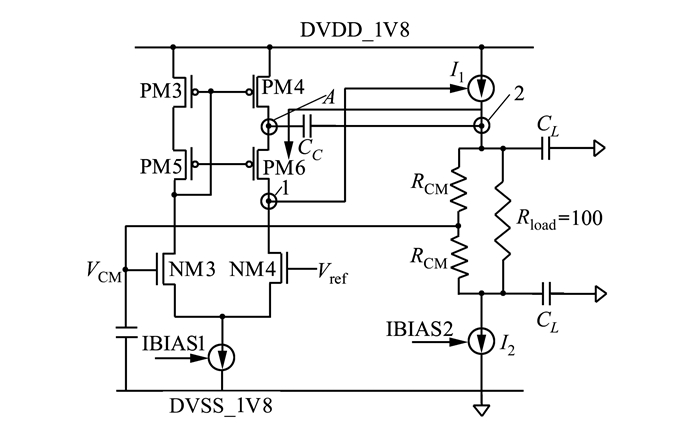

下面对LVDS驱动器采用沟道长度分割间接补偿法进行详细的小信号分析。图 8是LVDS发送器共模反馈环路小信号等效模型, 其中节点1对地的等效电阻为R1, 对地等效电容为C1; 节点2对地等效电阻为R2≈Rds‖RCM‖(Rload+RCM), 节点2对地电容为C2≈CL; 低阻节点A的等效电阻为1/gmp, 等效电容为CA。

|

| 图 8 共模反馈环路小信号等效模型 |

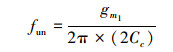

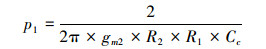

根据文献[13]中对2级运放沟道长度分割法小信号推导结论并结合LVDS驱动器实际小信号模型, 可推导得到LVDS发送器系统的零极点参数:

约定如下所示的符号含义:gm1为第一级运放输入管跨导, fun为单位增益带宽, A1为第一级增益, A2为第二级增益, A为2级总增益, z1为第一个零点, p1为第一个极点(主极点), p2为第二极点(输出极点), p3为第一级镜像极点。

|

(3) |

|

(4) |

根据小信号模型可知:第一级输出节点对地的等效寄生电阻和电容产生主极点

|

(5) |

第2个极点是由第一级运放电流镜镜像节点所贡献, 其中镜像节点对应的极点频率为

|

(6) |

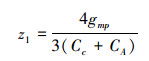

节点A对应的间接电流补偿反馈路径形成了系统零点

|

(7) |

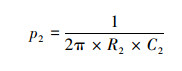

输出节点对地所对应的小信号寄生参数产生输出极点

|

(8) |

设计时是用节点A产生的零点与输出节点产生的极点进行了抵消, 也即上述所计算出z1和p2进行了零极点抵消。

3.2 共模检测电路共模检测电路部分采用电阻分压方式实现。为了使得高速数据传输过程中, 获得比较稳定的共模反馈电压, 需要将运放的单位增益带宽设计较高, 在容性负载一定的情况下, 需要将共模检测电阻设计较小, 以便将共模检测电阻对应的节点所贡献的极点推到单位增益带宽以外更高频率上, 同时不影响环路稳定性。基于上述分析, 本文为了充分利用共模检测电阻较小这一特点, 将传统的3.5 mA电流源设计为4.5 mA电流源, 也就意味着在高速数据传输过程中这额外1 mA也会对高速数据的高频分量进行补偿, 同时结合第4节所设计的预加重逻辑电路综合实现对高频分量的补偿, 从而提高高速数据传输时的信号完整性。

4 预加重逻辑产生电路设计预加重逻辑是用来产生与发送的数字信号同步且具有固定预加重时间宽度的脉冲信号, 预加重窗口时间长短是由要发送高速数据信号周期决定的, 理论上一般预加重窗口时间取为(1/5~1/8)×(1/f)比较适合。预加重窗口时间大小直接决定预加重电流的大小, 预加重窗口时间与预加重电流成反比, 因此需要根据系统设计指标和功耗约束选择合适的预加重窗口时间和预加重电流值, 本文设计是按照数据速率1.2 Gb/s, 理论上预加重窗口时间为(1/5)×(1/f)=167 ps, 实际按照200 ps进行设计。预加重电路是利用反相器、异或非门等组合逻辑电路设计实现, 预加重输入信号由所发送的高速数据信号产生, 预加重信号PRE_IN先经过由2个反相器组成的缓冲器电路, 然后一路直接输入到异或非门输入端, 另一路经过3个反相器组成的延时电路后输入异或非门输入端, 异或非门电路对输入的2路信号进行组合运算后得到与所发送的高速数据信号同步的预加重脉冲PRE_P和PRE_N, 然后分别驱动预加重功能电路中的状态切换开关S1和S2, 通过准确控制切换开关S1和S2的开关时间实现预加重功能, 图 9为设计的预加重逻辑功能产生电路。

|

| 图 9 预加重逻辑产生电路 |

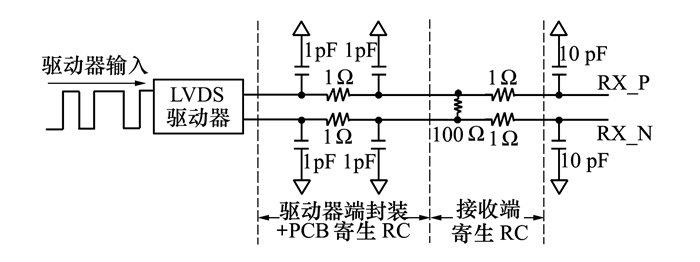

采用图 10所示的仿真测试模型对所设计的LVDS发送器进行功能仿真和验证, 其中发送器端寄生RC主要包括bond-wire和ESD的寄生电容约为1 pF、IO PAD寄生电容约为1 pF, PCB走线寄生电阻约为1 Ω、接收器端接负载阻抗和寄生电容分别为100 Ω和10 pF, 等效的总负载电容为12 pF。

|

| 图 10 LVDS驱动器仿真模型 |

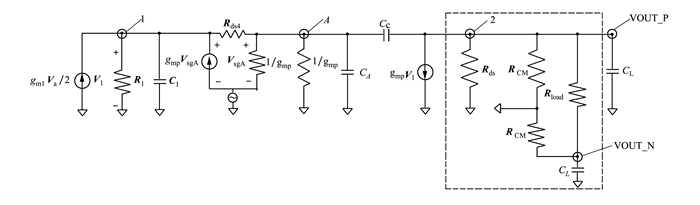

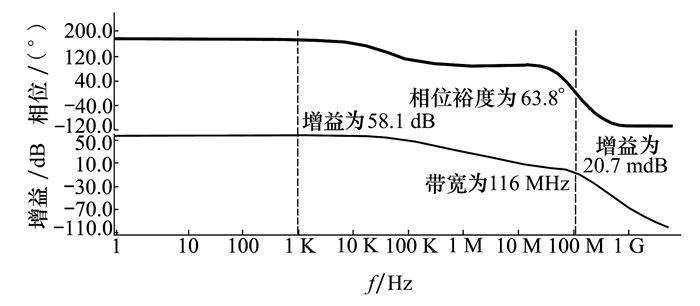

文中提出的LVDS驱动器电路共模反馈环路使用cadence公司的spectre仿真工具进行验证, 环路稳定性仿真结果, 包括低频增益、相位裕度及单位增益带宽等如图 11所示。

|

| 图 11 典型情况下环路增益和相位裕度 |

从图 11可以看出, 典型情况下LVDS驱动器低频环路增益为58.1 dB, 单位增益带宽达116 MHz, 相位裕度达到63.8°, 在保证高增益和相位裕度的同时极大提高了环路单位增益带宽。对设计的LVDS驱动器电路共模反馈环路进行Corner仿真结果如表 1所示。

| Corner | TT(27℃) | FF(27℃) | SS(27℃) | TT(125℃) | TT(-40℃) |

| 增益/dB | 58.1 | 68.2 | 42.5 | 46.4 | 62 |

| 相位/(°) | 63.8 | 60.5 | 56.3 | 68.2 | 65.6 |

从表 1的环路增益和相位裕度仿真结果分析可知:典型情况下低频环路增益为58.1 dB, 相位裕度为63.8°, 最差情况下(SS corner)低频环路增益为42.5 dB, 相位裕度为56.3°, 满足系统环路稳定条件。

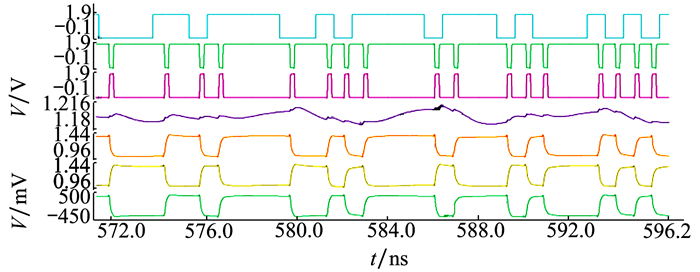

5.2 瞬态功能仿真结果当负载为12 pF时, 采用1.2 Gb/s伪随机码信号进行仿真测试, 得到的LVDS驱动器的输入输出信号波形如图 12所示:

|

| 图 12 LVDS发送器输出信号波形@1.2Gb/s |

图 12中波形从上往下分别表示发送的1.2 Gb/s伪随机码DIN、预加重信号(PRE_P和PRE_N)、共模信号、LVDS驱动器单端输出信号(LVDS_OUTP和LVDS_OUTN)及差分信号。从图中可以看出1.2 V共模信号VCM的最大纹波电压优于15 mV, LVDS驱动器差分信号Vod摆幅范围为+370 mV和-375 mV之间; 可看出所设计的LVDS驱动器在1.2 Gb/s速率时功能满足LVDS协议标准要求。

5.3 后仿真差分信号眼图文中提出的采用沟道长度分割方法设计LVDS驱动器在版图设计时需要注意两方面事项:①从不更改原有电路结构、晶体管尺寸参数及版图匹配性等三方面进行考量, 选择将需要沟道长度分割的CMOS晶体管的沟道长度进行二等分, 采取这种方式在版图阶段比较容易实现, 也是一种比较合理的实现方案。②从LVDS驱动器整体版图设计上来考虑, 由于LVDS驱动器传输的是高速差分信号, 在版图实现时要特别注意高速信号传输路径上信号走线的对称性和匹配性, 并尽可能降低高速差分信号链路金属走线带来的寄生参数对高频信号的干扰。首先, 采用Mentor公司的calibre验证工具对提出的LVDS驱动器整体版图提取寄生参数(包括寄生电阻、寄生电容等); 然后, 对包含所提取的寄生参数的电路网表再利用cadence公司spectre仿真工具进行仿真, 得到后仿真输出的高频差分信号; 最后, 利用spectre工具自带的眼图分析插件进行处理可得到图 13所示的眼图结果。

|

| 图 13 LVDS驱动器输出信号 |

图 13所示为1.2 Gb/s时的差分信号眼图, 从眼图可以看出, 差分信号摆幅统计均值分别为361.76 mV和-360.82 mV, 标准偏差分别为22.94 mV及13.94 mV, 周期抖动为19.86 ps, 具有较高的精度。

5.4 不同文献中驱动器性能对比表 2为本文所提出的LVDS发送器设计方案在驱动容性负载能力、传输速度、功耗及共模电压精度3个方面与相关文献中的LVDS发送器设计方案对比结果。表 2中Cload表示容性负载, Ptotal表示总功耗, ΔVcm表示共模反馈信号的变化。从表 2的对比结果可知:本文所提出设计方案在速度、功耗及共模电压精度3个主要性能指标方面均优于相关文献的设计。

通过以上仿真验证可看出,通过采用本文所提出的高速高精度低功耗LVDS驱动器设计方案,利用沟道长度分割间接补偿法既可以获得高增益又可以获得较高的带宽,并没有带来额外的晶体管面积和功耗开销,非常适合高速低电源电压下工作,同时共模电压的变化指标上获得了较高的精度,最大变化量不超过15 mV;另外采用了结构简单高效的预加重技术对高速信号的高频成分进行有效补偿,从而提高了发送器传输速率和信号完整性,最终的LVDS发送器所有模块总功耗为16 mW,对于负载电容大且对功耗要求严苛的高速高精度的应用场合,本文所提出的LVDS驱动器设计方案具有非常重要的工程应用价值和意义。

| [1] | GRACEFFA G A, GATTI U, CALLIGARO C. A 400 Mbps Radiation Hardened by Design LVDS Compliant Driver and Receiver[C]//2016 IEEE International Conference on Electronics, Circuits and Systems, 2016: 109-112 |

| [2] | YANG Zongxiong, LYU Xiaohua, LIU Huihua, et al. LVDS Driver Design for High Speed Serial Link in 0.13μm CMOS Technology[C]//2011 International Conference on Computational Problem-Solving, 2011: 145-148 |

| [3] | WONKI P, SUNG C L. Design of LVDS Driver Based CMOS Transmitter for a High Speed Serial Link[C]//2010 International Conference on Electronics and Information Engineering, 2010: 301-303 |

| [4] | NITHINNATH V K, SHEKAR G. An Area Efficient Termination Resistance Calibration Mechanism for LVDS Transceiver in 55 nm CMOS[C]//2017 International Conference on Microelectronic Devices, Circuits and Systems, 2017: 1-5 |

| [5] | Telecommunications Industry Association/Electronic Industries Alliance. Electrical Characteristics of Low Voltage Differential Signaling(LVDS) Interface Circuits[S]. TIA/EIA-644A, 2001 |

| [6] | IEEE Standards Association. IEEE Standard for Low Voltage Differential Signals(LVDS) for Scalable Coherent Interface[S]. 1596.3-1996 |

| [7] | CHEN M D, MARTINEZ J S, NIX M, et al. Low Voltage Low Power LVDS Drivers[J]. IEEE Journal of Solid State Circuits, 2005, 40(2): 472-479. |

| [8] | YEONG K C, YUNG M F, PENG K T, et al. 1.2Gb/s LVDS Interface[C]//2007 International Symposium on Integrated Circuits, 2007: 26-28 |

| [9] | WANG Xihu, WU Longsheng, LIU Youbao, et al. Low Power LVDS I/O Interface for above 2Gb/s Operation[J]. Journal of Electronics, 2009, 26(4): 525-531. |

| [10] | YANG Wang, WEI Xingai. Power Efficient Pre-Emphasis Method for Transmitters with LVDS Drivers[J]. Electronics Letters, 2014, 50(24): 1811-1813. |

| [11] | GE Xiaoliang. The Design of a Global Shutter CMOS Image Sensor in 110 nm Technology[D]. Delft: University Netherlands, 2012 |

| [12] | GIANLUCA T, FRANCESCO D C, VALENTINO L, et al. Design of LVDS Driver and Receiver in 28 nm CMOS Technology for Associative Memories[C]//2017 6th International Conference on Modern Circuits and Systems Technologies, 2017: 1-4 |

| [13] | VISHAL S, Indirect Feedback Compensation Techniques for Multi-Stage Operational Amplifiers[D]. Idaho: University Boise state, 2007 |

2. School of Microelectronics, Xi dian University, Xi'an 710065, China