水声信号主要有声呐信号、水下目标的回波信号、目标舰船的辐射噪声和海洋噪声信号等。在水声领域中,要实现对水下目标探测、定位以及水下目标通信,就需要对水声信号进行分析与研究。很多研究都需要长时间、高精度的获取声波信息,因此声信号采集系统的性能将直接影响到处理结果。现有的声学基阵常采用多元阵,基阵同时输出多路信号。这就需要设计一种多路同步的高精度信号采集存储系统来获取所需要的声波信息。目前已有的水声信号采集系统采样精度多为12, 16, 18 bit[1-6],可同步采集的通道数量多为固定的8, 12, 16路[7-13]。但是随着水声技术的不断发展,对水声信号采集系统也提出了更高的要求。例如系统功耗要足够低以维持超长时间的连续采集、可同步采集的通道数量要足够多、采集精度要足够高等。针对这些情况,设计了满足上述需求的信号采集系统,该系统功耗低至可维持长达一周的连续采集,可同步采集的通道数量多至64路,采样精度22 bit,配置方便可以随时修改采样频率与采样通道数量,且稳定可靠,可实现长时间连续稳定的多通道高精度信号采集和高速数据存储。

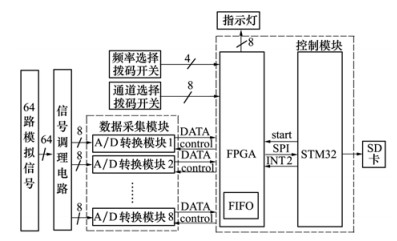

1 系统基本架构及原理采集系统主要由信号调理电路、数据采集模块、控制模块、SD卡等部分组成,系统硬件结构框图如图 1所示。

|

| 图 1 系统硬件结构框图 |

多路模拟信号进入系统,先经过放大滤波等信号调理,随后进入数据采集模块进行数模转换,接着经过FPGA内部的缓冲区,最终由STM32将其写入SD存储卡。频率选择拨码开关可选择当前系统的采样频率,通道选择拨码开关用来配置采集通道个数,开关控制8个A/D转换模块是否开启,并使对应的通道工作指示灯闪烁。

信号调理电路的作用主要是对待采集信号进行放大、滤波等操作使其转换成A/D芯片输入电压范围内的信号。

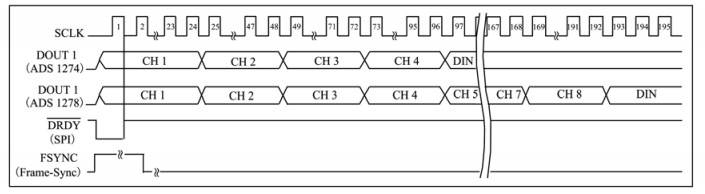

数据采集模块含有8块TI公司的8通道24位高精度模数转换模块ADS1278,共64路数据采集通道,可实现最高20 kHz的系统采样频率。ADS1278根据数字输入管脚MODE[1:0]与FORMAT[2:0]的状态配置工作模式与接口协议。在本系统中,MODE[1:0]=10,FORMAT[2:0]=001。此时,系统为低功耗模式,系统最大采样率为52.734 kHz,接口协议为SPI协议,数据输出模式为TDM(分时复用)。TDM模式指所有通道数据从单个管脚(DOUT1)输出,1通道数据先输出,8通道数据最后输出,所有通道数据均是高位先出,采用TDM模式的好处是可以减少系统硬件之间的连线,缩小版卡面积,其工作时序图如图 2所示。

|

| 图 2 ADS1278的TDM模式工作时序图 |

另外根据数据手册可以使A/D模块中工作时钟CLK与数据输出时钟SCLK共用同一个时钟信号,8个A/D模块共用同步信号(SYNC)。这样的设计在满足系统正常工作的情况下,占用I/O端口数量少,减少硬件连接的复杂程度。A/D与FPGA连接方式如图 3所示。

|

| 图 3 A/D与FPGA连接方式 |

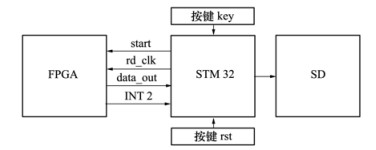

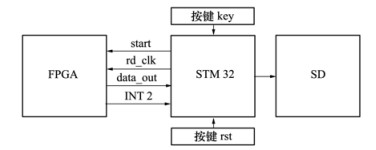

中央控制模块由FPGA与STM32共同组成。FPGA选用英特尔公司CycloneIV E系列的EP4CE10F22I7N;STM32则选用TI公司的STM32H743。FPGA根据频率选择拨码开关状态确定系统工作频率,根据通道选择拨码开关的状态判断开启的A/D转换模块,为其提供控制信号并使其对应的指示灯闪烁。在每个采样周期中FPGA读取A/D量化后的数据并将其按通道顺序写入内部的一位FIFO进行缓存。每写满一帧(512×24 bit)数据,向STM32发出中断信号INT2。STM32检测到中断信号之后通过SPI总线(rd_clk与data_out)读取FPGA缓冲区中的数据,然后写入大容量SD存储卡中。STM32与FPGA之间有多种数据传输方式以减少硬件连线。本系统采样串行数据传输方式,在64通道同时工作并且采用率为20 kHz时,串行接口的数据量为100 Mb/s。FPGA与STM32连接方式如图 4所示。

|

| 图 4 FPGA与STM32连接方式图 |

SD存储卡卡具有小巧轻便、存储容量大、传输数据快和数据安全性高等优点。选用支持SD3.0协议的SDXC卡作为系统的存储卡。

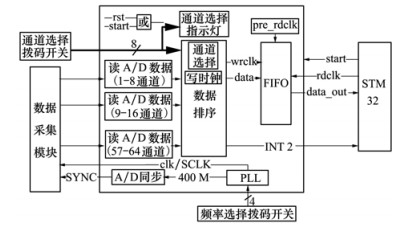

2 FPGA关键逻辑实现FPGA是多通道采集存储系统的关键,负责为A/D模块提供控制信号、读取A/D转换模块的输出信号、将信号存入FIFO等。FPGA内部逻辑框图如图 5所示。

|

| 图 5 FPGA内部逻辑框图 |

锁相环PLL倍频晶振时钟至400M作为FPGA内部工作时钟。另外,由数据手册可知ADS1278的采样频率为其工作时钟频率的

A/D同步模块为系统数据采集模块中的A/D芯片提供同步信号SYNC。由数据手册可知同步信号SYNC的上升沿用以同步所有正在工作的A/D芯片。因此该模块将仅在上电后输出一个脉冲其余时间均保持低电平输出。

通道选择拨码开关可控制A/D芯片是否工作。拨码开关与A/D芯片一一对应,当开关开启时,FPGA向对应的A/D提供CLK信号,此时A/D芯片工作;开关关闭时,FPGA停止向对应的A/D提供CLK信号,则A/D芯片停止工作。通道选择指示灯模块根据开关的状态使对应的指示灯闪烁。

读A/D数据模块读取一片A/D采样芯片转换完成的数据。在每个采样周期中,当A/D芯片给出采样完成标志DRDY后,每当CLK上升沿来临FPGA读入一位数据,将其写入24位寄存器变量data_buffer的最低位并左移一位。每读满24位也就是一个通道的数值,将其输出至数据排序模块等待排序。重复此过程直至读完8个通道的数据,此时给出完成标志位get_done并进入等待模式直至下一个DRDY信号来临。

数据排序模块在每个采样周期中会根据通道选择拨码开关的状态判断正在工作的A/D模块。在收到所有读A/D模块的完成标志位后产生FIFO的写时钟信号。将这一采样周期内转换完成的数据按通道标号由小至大的顺序写入FIFO,没有工作的通道跳过。

FIFO是为增加数据传输效率、处理大量数据流、匹配具有不同传输率的系统而广泛使用存储器。本系统中使用深度为32 764 bit的1位异步FIFO来作为数据缓冲。将FIFO的写使能wrreq和读使能rdreq端口始终拉高,仅通过控制读时钟rdclk和写时钟wrclk来控制FIFO数据的读写。每个写时钟上升沿来临就向FIFO中写入一位数据,当打开全部通道、采样频率20 kHz时,每个采样周期为50 μs,输出数据时钟周期为

FPGA的复位由外部按键rst及STM32提供的start信号共同控制。复位时FPGA内部FIFO及计数器清空、其余模块恢复初始状态。

pre_rdclk模块是根据异步FIFO的特性和其在实际应用中的情况而设置的。pre_rdclk模块在中断信号INT2发出之后,读时钟rdclk来临之前,产生3个时钟周期的脉冲信号至FIFO的读时钟引脚从而保证rdclk的每一个上升沿都可以读取有效数据。

3 单片机工作流程单片机作为SD存储卡的控制芯片,在系统中起着重要的作用。其外围电路框图如图 6所示,与STM32相连的器件有FPGA、SD存储卡、复位按键rst、工作按键key。

|

| 图 6 STM32外围电路框图 |

系统上电后首先初始化单片机并延时100 ms等待系统稳定,随后通过start管脚使FPGA处于复位状态并关闭单片机中的中断响应,接着初始化SD存储卡及其文件系统、创建文件并延时2 s,然后使能FPGA并开启中断响应,此时系统准备就绪。单片机工作流程图如图 7所示。

|

| 图 7 单片机工作流程图 |

中断子程序一旦检测到中断信号INT2,立即从FPGA中读取一帧数据,判断数据标志位并将其存入缓冲区。单片机中设置2个64 k大小的缓冲区,数据轮流存入缓冲区1和缓冲区2,当缓冲区1满,标志位b1=1,数据开始存入缓冲区2;当缓冲区2满,标志位b2=1,数据开始存入缓冲区1。双缓冲区与单缓冲区相比更具优势,避免了在缓冲区数据还未写入SD卡时,新的一帧数据来临覆盖之前的数据,造成SD卡存储错误的情况。数据进入缓冲区的速率为50 Mbit/s,采用四线模式写入SD卡,写入时钟速度12.5M即可满足要求。为给初始化、写命令等其他操作预留时间,SD卡时钟取50M。

主程序在工作开关key开启之后,检测到b1=1,将缓冲区1中的数据写入SD存储卡并将b1置0;检测到b2=1,将缓冲区2中的数据写入SD存储卡并将b2置0。由于采样数据率小于SD卡写入速率,因此不存在2个缓冲区同时满的情况。

4 系统分析与实验为测试系统的性能以及说明一些关键性参数的选择依据。在实验室搭建采集系统并进行实验。

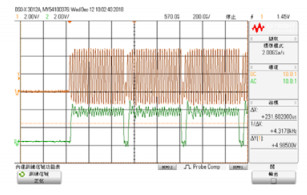

4.1 关于FIFO的实际应用将写入FIFO的数据设置为固定数,读取数据,观察FPGA与STM32的SPI接口的时钟数据波形,发现SPI接口的数据总是比时钟延迟2个时钟周期。查看数据手册,发现这种现象是由FIFO的特性决定的。通常情况下,向FIFO中写数据时,当写使能为高,写时钟的第一个上升沿,数据就可以写入FIFO。但是需要特别注意的是,从FIFO中读取数据时,当读使能为高,读时钟的第二个周期之后才有有效数据输出。因此设计了pre_rdclk模块,pre_rdclk模块将在rdclk信号来临之前产生2个时钟周期的脉冲信号。

查看写入SD卡的数据却发现与实际固定数不符,进一步观察发现SD卡中的数据与原数据发生错位。经过分析可知,FPGA芯片特性决定了其内部从接收信号到做出反应需要一定的(本文选用的EP4CE10F22I7N需要约7 ns)应答时间,因此在收到rdclk的上升沿与FIFO输出数据之间会有一个短暂的时间延迟。但是STM32在rdclk上升沿时就已经读取数据。此时STM32读取的数据为上一个时钟周期输出的数据,这就造成了读数据错位。因此在pre_rdclk模块中再增加一个时钟周期的脉冲信号以保证在rdclk的每个上升沿STM32均可以读取正确有效的数据(pre_rdclk模块最终产生3个时钟周期的脉冲信号)。实验中,当固定数为0X7FFFFF时,STM32与FPGA的SPI接口时钟数据图如图 8所示。

|

| 图 8 FPGA与STM32的SPI接口时钟数据图 |

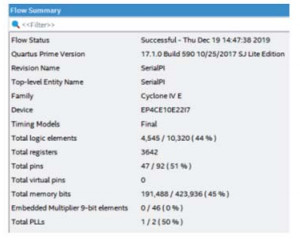

FPGA完成逻辑占用的各项资源如图 9所示。除未使用乘法器以外其余资源均使用50%左右。逻辑资源占用情况较为合理,留有充足的余量支持SignalTap调试以及今后功能扩充。

|

| 图 9 FPGA资源占有率 |

对系统各部分功耗进行分析。系统使用的单片机型号STM32H743,其工作时内部时钟300 MHz。在外部设备全部工作情况下工作电流170 mA,在外部设备全部禁用情况下工作电流72 mA。本系统中仅使用SPI接口和SD卡接口。估计电流约为85 mA,因此功率约为283 mW。

使用功耗分析工具(power play early power estimator)对FPGA的功耗进行分析。编译文件后生成.csv文件。在功耗分析工具中导入即可自动计算FPGA功耗。本系统FPGA功耗为0.092 W。

每个通道A/D转换芯片功耗约30 mW,64通道同时工作时总功耗约为1.920 W。

系统中电压转换芯片MP2359效率92%,功耗约为0.326 W。单路模拟电路所用运放功率消耗估计值如表 1所示。分别为0.002和0.1 W。计算可得系统总功率约为3.389 W。

在系统上电后工作后进行测量,供电电压为12 V。仅测量数字版时电流0.085 A,功率约1.02 W。系统满负荷工作时测得电流0.340 A,总功耗4.08 W。比计算多出的部分值估计为PCB传输线损耗及其余电子器件工作功率。

4.4 系统的稳定性优化在测试中发现,系统长时间连续工作(十几小时)后, 偶尔会出现数据错位。分析可知在单路FIFO中,数据从FPGA读入到单片机时,总线速度最高可达100 Mb/s,数据快速读写,偶尔丢失或者重复读取一位数据,导致后续所有数据错位。本文设计了如下解决方案,在FPGA中将每个通道24位采样数据的最低两位置为1,STM32每读取一帧数据,检测第一个24位数据的末2位。若全为1则系统正常运行,若不全为1则表明数据出现错位,此时STM32将FPGA的start管脚置低,FPGA复位,FIFO被清空,其余模块恢复初始状态。延时10 ms后FPGA重新开始工作。

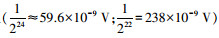

采用上述方法使得实际的采样精度只有22位。但由于24位与22位A/D采样的精度均在纳伏(nV)级(

开启全部64通道,设置A/D模块采样频率为20 kHz。通过函数发生器向1至63通道输入频率500 Hz,峰峰值1.0 V的正弦信号,第64通道短路。系统运行一段时间后,从SD卡中导出数据并利用Matlab绘制1通道至64通道接收到的信号的时域波形图,如图 10所示。

|

| 图 10 1通道与64通道信号时域波形图 |

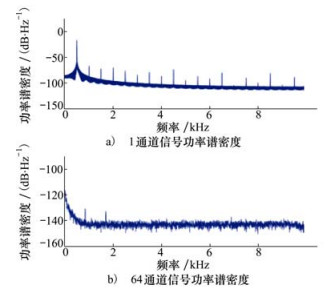

观察可得1通道至63通道的信号时域波形相同,均为无失真正弦信号,峰峰值略小于1.0 V,分析原因可能是模拟调理通路的衰减。第64通道是采集的系统自噪声,经过计算,其噪声均方差为14.3 μV,表明采集系统的具有很小的底噪,可以保证采集信号的信噪比。1通道与64通道的频谱图,如图 11所示。

|

| 图 11 1通道与64通道信号频谱图 |

从图 11中可以看出,1通道采集的正弦信号频谱峰值横坐标为500 Hz,与输入信号的频率一致。在其余频段上分布着较小的波纹。64通道采集的有色噪声在频谱上,具有低频幅度大,高频幅度小的特点,符合电子电路低频噪声幅度大的特性。

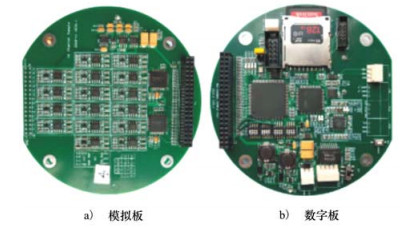

另外经验证系统拨码开关、指示灯等均正常工作。系统可以正常运行。系统模拟板和数字板如图 12所示。系统实物图如图 13所示。

|

| 图 12 系统模拟板和数字板实物图 |

|

| 图 13 系统实物图 |

信号采集系统应用十分广泛,有许多科研机构和公司均推出了相关产品。分析可知各类采样精度多为12, 16, 18 bit,可同步采集的通道数量多为固定的8, 12, 16路。当然也有公司推出了性能非常好的采集系统。例如,西安虹陸洋机电设备有限公司推出一款96通道信号采集系统,最大采样率96 kHz,存储介质为4张SD存储卡,系统功耗20 W,除去电池,电路板体积约ϕ124 mm×450 mm。

若将本系统升级为96通道96 kHz采样系统,与之进行对比。按照本系统构成,需增加2块采集板,系统体积ϕ100 mm×150 mm。与之相比通道数量相同的情况下体积较小。估算升级后系统功耗。将ADS1278配置为高速模式,功耗70 mW/h。估算控制芯片功耗为数据手册给出的最大功耗,STM32为2.772W,FPGA为1.5 W。实际中,加上PCB传输线损耗以及其余器件功耗。估算系统总功率约为15 W。因此,本系统当前性能与之相比有差距但依然具有自己的优点。

5 结论本文设计了基于FPGA与STM32的工作通道数量和采样频率可变的多通道信号采集存储系统。充分利用了FPGA与STM32器件的特点,并综合分析多方面影响因素,针对FIFO的特性进行相应操作,为提高系统稳定性增加数据校验步骤。使系统各部分相互配合,经过仿真验证、实际测试,得到了稳定可靠、低功耗、低成本的采集存储系统。整个系统具有很强的通用性,可以广泛应用于各种多路的信号采集系统中。

| [1] |

张云鹏.声纳浮标数据采集系统的设计与实现[D].哈尔滨: 哈尔滨工程大学, 2017 ZHANG Yunpeng. Design and Realization of the Sonobuoy Data Acquisition System[D]. Harbin: Harbin Engineering University, 2017(in Chinese) https://www.ixueshu.com/document/79da8b70f0a1bdba4058e7f371481993318947a18e7f9386.html |

| [2] |

高正杨.多通道水声信号采集系统设计与实现[D].哈尔滨: 哈尔滨工程大学, 2015 GAO Zhengyang. Design and Implementation of Multi-Channel Acoustic Signal Acquisition System[D]. Harbin: Harbin Engineering University, 2015(in Chinese) 通道水声信号采集系统设计与实 |

| [3] |

李雷.基于FPGA的水声基阵信号采集与传输技术[D].哈尔滨: 哈尔滨工程大学, 2015 LI Lei. Underwater Acoustic Array Signal Acquisition and Transmission Technology Based on FPGA[D]. Harbin: Harbin Engineering University, 2015(in Chinese) http://cdmd.cnki.com.cn/Article/CDMD-10217-1018051833.htm |

| [4] |

陈晓辉.水声信号采集记录仪设计与实现[D].哈尔滨: 哈尔滨工程大学, 2015 CHEN Xiaohui. Design and Implementation of Underwater Acoustic Signal Acquisition Recording Instruments[D]. Harbin: Harbin Engineering University, 2015(in Chinese) |

| [5] |

黄紧德. 多路完全同步采样的声信号采集系统的设计与实现[J]. 软件, 2013, 34(2): 17-21.

HUANG Jinde. Design and Implementation of Multiple Fully Synchronized Sampling Acoustic Signal Acquisition System[J]. Software, 2013, 34(2): 17-21. (in Chinese) DOI:10.3969/j.issn.1003-6970.2013.02.006 |

| [6] |

刘建明.高精度水声信号采集回放模块电路的设计与实现[D].成都: 电子科技大学, 2012 LIU Jianming. The Design and Implementation of High-Precision Underwater Acoustic[D]. Chengdu: University of Electronic Science and Technology of China, 2012(in Chinese) |

| [7] |

张耀政, 王文廉, 张志杰. 基于单路FIFO的多通道同步采集存储系统的研究[J]. 电力系统保护与控制, 2010, 38(8): 100-104.

ZHANG Yaozheng, WANG Wenlian, ZHANG Zhijie. Study on Multi-Channel Synchronization Acquisition and Storage System Based on One FIFO[J]. Power System Protection and Control, 2010, 38(8): 100-104. (in Chinese) DOI:10.3969/j.issn.1674-3415.2010.08.022 |

| [8] |

洪蕾, 钟睿. 船舶航行信号数据多通道并行采集系统设计[J]. 舰船科学技术, 2018, 40(14): 190-192.

HONG Lei, ZHONG Rui. Design of Multi-Channel Parallel Acquisition System for Ship Navigation Signal Data[J]. Ship Science and Technology, 2018, 40(14): 190-192. (in Chinese) |

| [9] |

刘楠. 水声信号处理系统的应用与研究[J]. 信息通信, 2018(6): 59-60.

LIU Nan. Application and Research of Underwater Acoustic Signal Processing System[J]. Information & Communications, 2018(6): 59-60. (in Chinese) DOI:10.3969/j.issn.1673-1131.2018.06.023 |

| [10] |

马雪. 基于FPGA嵌入式设计的水声信号采集系统[J]. 舰船电子工程, 2017, 37(3): 135-139.

MA Xue. Underwater Acoustic Signal Acquisition System Based on FPGA Embedded Design[J]. Ship Electronic Engineering, 2017, 37(3): 135-139. (in Chinese) DOI:10.3969/j.issn.1672-9730.2017.03.033 |

| [11] |

谢旭良, 刘纪元, 陈新华. 基于DSP和FPGA的多通道水声信号采集[J]. 网络新媒体技术, 2016, 5(4): 30-35.

XIE Xuliang, LIU Jiyuan, CHEN Xinhua. Multi-Channel Underwater Acoustic Signal Acquisition Based on DSP and FPGA[J]. Journal of Network New Media, 2016, 5(4): 30-35. (in Chinese) DOI:10.3969/j.issn.2095-347X.2016.04.005 |

| [12] |

项顼.水声信号采集模块研制[D].青岛: 中国海洋大学, 2015 XIANG Xu. The Sound Signal Acquisition Module Design of Underwater Acoustic Communication[D]. Qingdao: Ocean University of China, 2015(in Chinese) |

| [13] |

苏军, 尚凡. 四路同步水声信号记录仪设计与实现[J]. 电子世界, 2013(17): 147-148.

SU Jun, SHANG Fan. Design and Implementation of Four-Channel Synchronous Underwater Acoustic Signal Recorder[J]. Electronics World, 2013(17): 147-148. (in Chinese) DOI:10.3969/j.issn.1003-0522.2013.17.109 |