2. 中航工业西安航空计算技术研究所, 陕西 西安 710065

超大规模计算对内存的需求量将是目前容量的1 000倍以上[1],但DRAM特征尺寸的缩小也变得越来越困难。原因是在缩小DRAM特征尺寸时,为了保证电荷的保持时间,电容值必须达到25 fF,致使电容的物理结构变得极不对称,特别当特征尺寸达到20 nm时,电容的高度与底面直径的比值将超过100,细长的几何结构会使电容器更易受到损坏,从而降低了可靠性,同时也加大了生产制造的难度[2]。另外,随着特征尺寸的缩小,DRAM漏电流将急剧增大,导致静态功耗不断增大,从而增大了整体功耗。

幸运的是,新型的相变存储器(phase change memory, PCM)具有很好的扩展性,并且漏电功耗非常低,因为它利用相变材料在不同状态下电阻值的不同来存储数据。与DRAM相比,PCM具有以下几个优势:(1) 存储密度大;(2) 属于非易失性存储器,不需要刷新;(3) 漏电流很小;(4) 几乎不受软错误的影响。这些优势使PCM成为替代DRAM有力的竞争者。但是使用寿命较短是PCM的一个严重问题。一般认为DRAM存储单元几乎可写入无限次(1016次),而PCM可写次数只有108次[3]。所以,必须采取有效措施来延长其使用寿命,增强PCM内存的可靠性。为此,需要尽量减少对PCM存储单元的写操作,同时尽量将写操作均匀分布在所有PCM存储单元上[4]。

当前一般采用DRAM和PCM构成混合内存的方法,来减少对PCM的写操作,混合内存主要有2类结构。第一类由DRAM和PCM共同构成物理存储空间,将频繁使用的数据交换至DRAM中,而DRAM中不经常使用的数据将被交换至PCM中。Gaurav Dhiman等人提出的PDRAM[5]中,以页(page)为单位,在DRAM和PCM间进行数据交换。在内存控制器中增加了一个访问统计表,如果PCM中某一页的写操作次数达到一个阈值,则由操作系统调度页面,在PCM和DRAM间进行交换。该方法以页为单位进行数据迁移,延迟和功耗都比较大。HanBin Yoon等提出了基于行缓冲区命中率的交换策略[6],以存储阵列的行(row)为单位进行数据交换,分别对DRAM和PCM的行缓冲区命中率进行统计,将命中率高的数据行交换至PCM中,而将命中率较低的数据行交换至DRAM中,以此来提高PCM行缓冲区的命中率,减少对PCM存储阵列的写操作次数。然而,有些程序中数据的局部性较差,会导致数据预测的准确度较低。第二类将DRAM作为PCM的Cache使用,例如Moinuddin K.Qureshi等人提出,将DRAM作为PCM片外Cache的混合内存结构[7],可以减少对PCM写操作的次数,同时降低整体写操作的延迟和功耗。在该结构中,DRAM替换出的脏数据越少,对PCM写操作的次数就越少,PCM的寿命就越长,而替换出脏数据的数量,受替换策略的影响较大。为了进一步减少对PCM写操作的次数,Sung Kyu Park等人提出了新的替换算法[8],进一步减少了对PCM写操作的次数,延长了PCM内存的寿命。

通过上述分析可知,DRAM作为PCM片外Cache结构的性能相对较好,但也存在一些问题,根本原因在于未区分读操作和写操作的不同影响。读操作不会缩短PCM的寿命,同时PCM读操作功耗比DRAM读操作功耗低;而写操作会对PCM的寿命造成影响,同时写操作的延迟和功耗都比较大。由此可见,DRAM应尽量缓冲存储写操作的数据,以减少对PCM写操作的次数。为此,本文中提出将DRAM作为PCM主存的写操作数据Cache的结构。

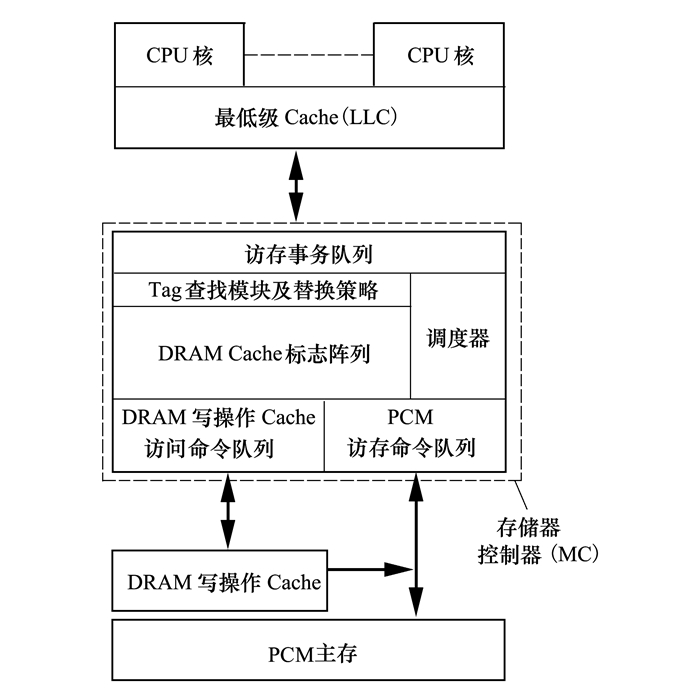

1 写操作Cache结构及调度策略 1.1 总体结构及调度在使用DRAM写操作Cache的PCM主存结构中,DRAM只存储来自最低级Cache(last level cache, LLC)写操作的数据,不会将读操作的数据存储在DRAM中。通过这种方法,在DRAM存储空间有限的情况下,可以提高写操作的命中率,从而减少了对PCM写操作的次数,可有效地延长其寿命。同时,这种结构也消除了读操作对寿命影响的问题。其整体结构如图 1所示。

|

| 图 1 整体架构 |

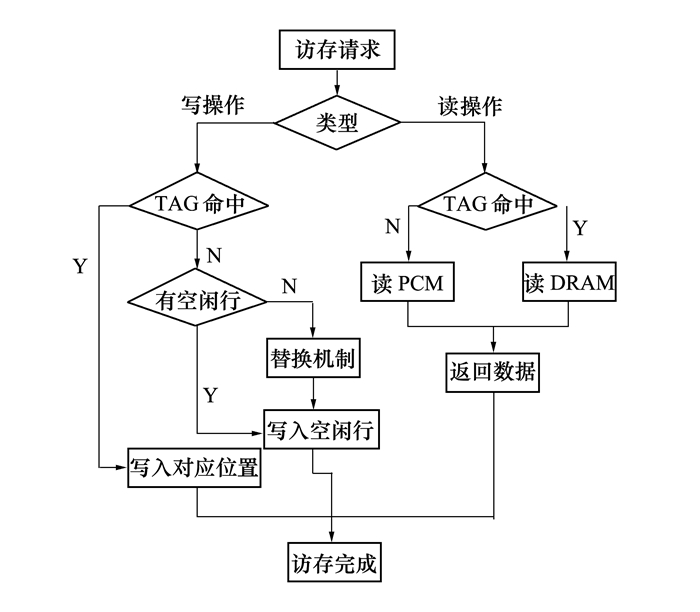

在该结构中,DRAM Cache的标志域(Tag)位于存储器控制器(memory controller, MC)中。MC对读操作和写操作的处理方法不同,对应的数据通路也不同。当MC接收到写操作请求时,首先查找Tag域,并判断写DRAM Cache是否命中。如果命中,则直接将数据写入DRAM Cache中对应位置即可;如果未命中,则需要在DRAM Cache中为该数据分配一行存储空间,并且根据是否有合适空闲行来确定是否需要进行Cache块的替换。由于DRAM Cache只存储写操作的数据(即脏数据),因此在被替换出去时,需要写入PCM中。相对于PCM来说,DRAM Cache中的数据为最新数据。

当MC接收到读操作请求时,同样先查找Tag域,如果Cache命中,则直接读DRAM Cache即可得到最新的数据,不需要再对PCM进行访问。否则,所请求的数据不在DRAM Cache中,对PCM进行读操作就可以得到最新数据。与传统DRAM Cache混合存储器不同,从PCM中读到的数据不需要再写入DRAM Cache中,只需要返回给CPU即可。基于DRAM写操作Cache的PCM主存调度策略如图 2所示。

|

| 图 2 调度策略 |

由调度策略可知,DRAM Cache中并不存储从PCM中读取的数据,因此在DRAM Cache存储空间有限的情况下,可以过滤更多的写操作,从而减少对PCM写操作的次数,延长PCM的寿命。

除了减少PCM写操作次数,以提升混合存储器寿命外,DRAM写操作Cache也可有效提升读写操作的性能。由于PCM写操作的延迟和功耗都远远大于DRAM,因此在减少PCM写操作次数的情况下,内存的整体写操作延迟和功耗都将极大降低。对于读操作,在该结构中,如果数据在DRAM Cache中,则读操作延迟和功耗与DRAM相当。如果数据在PCM中,读操作的延迟和功耗与PCM相当。因此,在该结构中,读操作延迟至多与PCM读操作延迟持平,读操作功耗至多与DRAM读操作功耗持平。而在传统混合存储器结构中,最大读操作延迟及功耗均为两者之和,因此该结构还将有效地提升读操作的性能。

1.2 基于DRAM写操作Cache的PCM主存数据通路当MC接收到访存请求时,将其加入事务队列(Transaction Queue)中,之后通过调度机制将队列中的访存请求转化为访存命令,并发送到DRAM Cache或PCM的访存命令队列中。在将访存请求转化为访存命令时,需要先对访存类型进行判断。访存类型可以通过事务类型(Transaction Type)得到,它有3种取值:DATA_READ,DATA_WRITE和RETURN_DATA。其中,DATA_READ表示该访存请求为读操作;DATA_WRITE表示写操作;RETURN_DATA表示读操作得到的数据。通过事务类型得到访存类型后,就可以根据访存类型,将对应的访存命令加入DRAM Cache或PCM的访存命令队列中。

1.2.1 DRAM Cache的Tag域访问与传统Cache类似,DRAM Cache的Tag域中也需要存储Tag值、有效位、替换策略位等。然而,DRAM写操作Cache中全部是脏数据,因此不需要dirty位。

基于DRAM写操作Cache对Tag域的访问与DRAM存储体的访问串行操作,只有当访问Tag域命中时,才会对DRAM Cache存储体进行访问。对DRAM Cache进行访问时,需要得到对应数据在DRAM Cache中的地址,通过该地址对DRAM Cache进行读操作。由于Tag值的索引与DRAM Cache地址空间存在一对一的关系,即Index和DRAM Cache地址空间存在固定的映射关系,因此在判断Tag域命中时,可以根据所在组号、组内块号生成DRAM的访问地址D-addr。

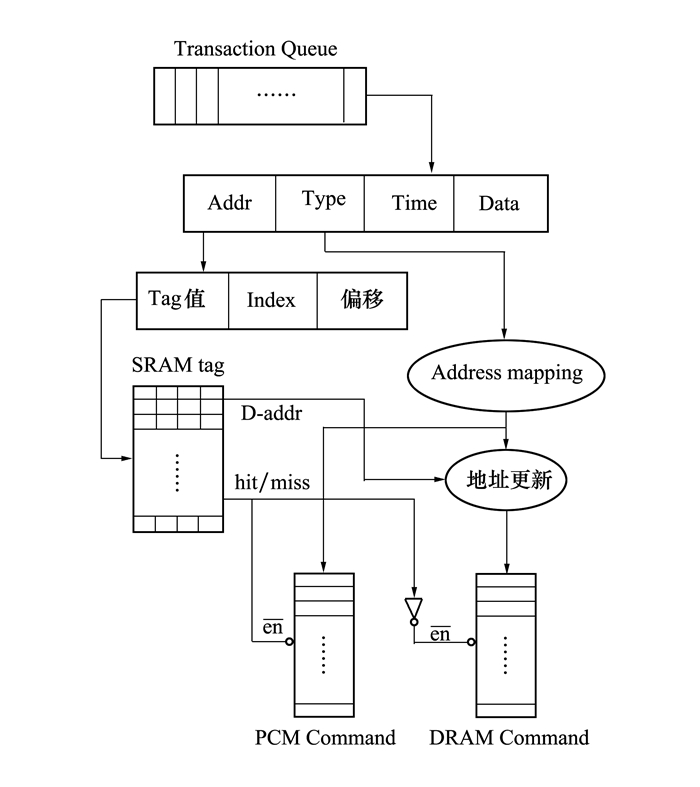

1.2.2 读操作数据通路基于DRAM写操作Cache的PCM主存读操作过程如下:

首先访问Tag域,如果命中则表示读操作请求的最新数据在DRAM Cache中,同时也可以得到数据在DRAM Cache中的地址A,此时将访存请求解析为DRAM Cache的访问命令,并加入到DRAM Cache对应的命令队列(Command Queue)中等待调度。由于原始访存请求中的地址B是针对PCM存储空间的地址,而在访问DRAM Cache时需要使用Tag域中存储的DRAM访存地址A,因此在对DRAM Cache进行访问前,需要在地址A和B之间建立映射关系。当通过地址A访问DRAM Cache得到数据时,将数据返回给地址为B的访存请求。

当Tag域未命中时,表明读操作请求的数据在PCM中,此时不需访问DRAM Cache,而直接访问PCM。由于访存请求中的地址为PCM存储空间的地址,可直接将访存请求解析为PCM访存命令,并加入PCM的Command Queue中。

当DRAM Cache或PCM中对应读操作请求完成后,将读到的数据构建一个RETURN_DATA型的事务,并加入到返回事务队列(return transaction queue)中,之后发送给CPU。基于DRAM写操作Cache的PCM内存读操作数据通路如图 3所示。

|

| 图 3 读操作数据通路 |

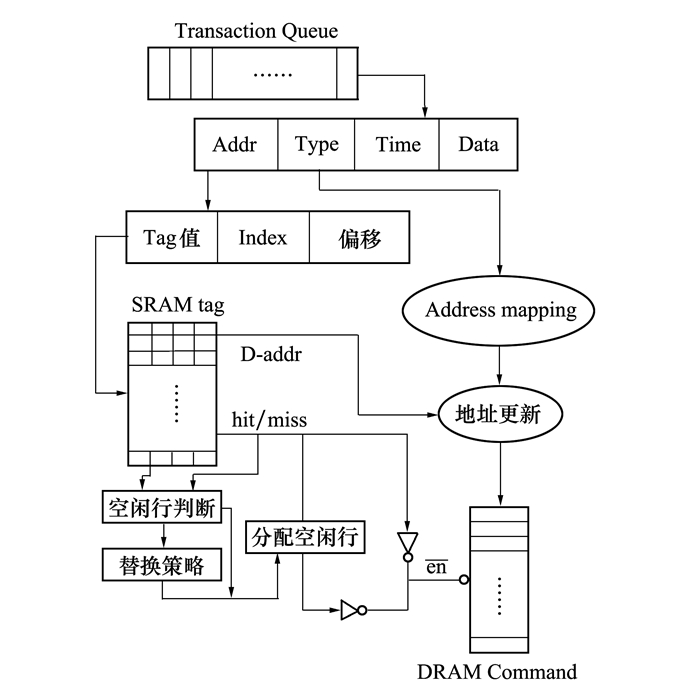

基于DRAM写操作Cache的PCM主存写操作数据通路如图 4所示。

|

| 图 4 写操作数据通路 |

当访存请求类型为DATA_WRITE时,同样先访问Tag域。如果命中,则表明DRAM Cache中已经为该地址分配了存储空间,且存有旧数据,此时只需要将写操作请求中的新数据写入DRAM Cache中即可。在对DRAM进行写操作之前,先通过Tag域和DRAM Cache地址空间的固定映射关系,变换得到DRAM Cache的地址D-addr。将原始PCM写操作的地址更新为DRAM Cache的访问地址D-addr,并将该访存请求转化为DRAM Cache的写操作命令,加入到DRAM Cache的Command Queue中等待调度。

当访问Tag域未命中时,表示第一次对该地址进行写操作,或该地址对应数据已经被替换到PCM中,此时DRAM Cache中没有该地址对应的存储空间,需要在DRAM Cache对应组(set)内为该地址分配空闲行。如果该组内存在空闲行,则在将数据写入DRAM Cache的同时更新Tag域。

当访问Tag域未命中,同时Tag域该组内没有空闲行,此时需要根据替换策略将某一行数据替换出去,之后再将该空闲行分配给本次写操作请求。由于DRAM Cache只接收来自CPU写操作的数据,因此从DRAM Cache中替换出的所有数据都必须写入PCM中,以保证数据的正确性。此时写操作的步骤为:(1) 找到替换行;(2) 对DRAM Cache进行读操作;(3) 被替换的行写入PCM;(4) 将本次写操作请求的数据写入该空闲行中,并更新相应的Tag域。

1.3 DRAM写操作Cache的替换策略传统Cache的替换策略一般采用最近最少使用(least recently used, LRU)算法或伪LRU算法,只是简单地将最近最少使用的数据替换出去,并没有考虑到写操作的频繁程度,因此可能将写操作次数较多、但时间间隔长的数据替换出去,导致数据频繁地被替换出去,增加了对PCM写操作的次数,影响其寿命。因此本文提出了一种基于写操作频率的替换策略。

在该替换策略中,当需要替换出Cache行时,首先选择最近一段时间窗口内写操作次数最少的数据块,将该Cache行替换出去并写入新数据。如果多个Cache行写操作次数相同,便采用LRU算法,将最早进行写操作的Cache行替换出去。

在基于写操作频率的替换策略中,写操作次数最少的数据块最先被替换出去,这样就可以避免写次数较多的数据块被频繁替换出去。在DRAM Cache容量受限的情况下,可以有效地提高DRAM Cache的命中率,减少对PCM的写操作次数。

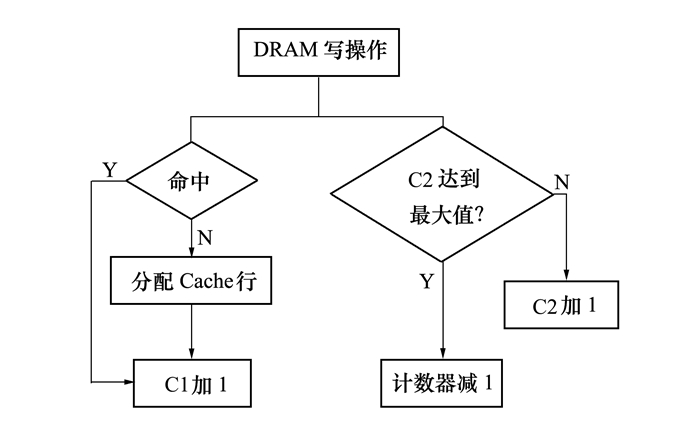

为了统计数据块的写操作次数,在组内的每一行Tag域增加一个写操作饱和计数器。初始状态时计数器的值为0,当数据块刚被写入DRAM写Cache中时,保持其计数器的值不变。在数据写入DRAM之后,如果再次对该数据进行写操作,就需要更新其写操作次数,即将对应的计数器加1。当计数器达到最大计数值后,如果再次对其进行写操作,就将计数器保持在最大值状态。在一定时间窗口内后,需要对所有饱和计数器进行减1操作,当某一计数器值减为0时,就将该计数器保持在0状态。在实现中,对每个Cache行增加一个3位饱和计数器C1,同时为每组增加一个3位饱和计数器C2。当对Cache进行写操作时,将该行对应的饱和计数器C1加1,同时将该组的3位饱和计数器C2加1,当饱和计数器C2达到最大值时,将该组内所有饱和计数器值减1。对DRAM进行写操作时,对饱和计算器的处理如图 5所示。

|

| 图 5 饱和计数器的处理 |

当写DRAM缺失时,如果对应组内有空闲行,则直接将数据写入空闲行;如果该组没有空闲行,则将计数器值最小的数据块替换出去,同时写入新数据,并将其计数器值更新为0。如果多个计数器值相等且均为最小值,则采用“伪LRU”算法,将最近最少使用的数据块替换出去,考虑到替换策略的复杂度,此时也可以采用随机替换策略来加快速度,降低硬件开销。

2 仿真评估 2.1 仿真环境我们使用GEM5体系结构仿真器模拟多核CPU,并通过运行所选择的基准测试程序,收集对内存的访存请求,保存为踪迹文件,之后由内存仿真器读取踪迹文件,并响应访存请求,以此来统计存储器的性能参数。

在实验中,通过GEM5模拟了8核CPU,每个核拥有单独的L1数据Cache(32kB, 8路组相联)和指令Cache(32kB,4路组相联),并共享L2 Cache(2MB,8路组相联), PCM的容量为16GB,访存请求队列和访存命令队列的深度均为32,访存调度采用rank_then_bank_round_robin,行缓冲器管理采用开策略。由于PCM的寿命与访存密集程度有很大关系,因此实验过程中,8个CPU核运动同样的测试程序,以此来增加对内存的访问。同时为了分析基于DRAM写Cache的PCM主存的性能优势,实验中分别搭建了3组实验环境:(1)PCM直接作为内存;(2)DRAM作为PCM读写Cache;(3) DRAM作为PCM写操作Cache,通过运行相同的测试程序,对比分析了3种结构的可靠性及访存性能。

2.2 仿真结果及分析 2.2.1 PCM主存寿命分析PCM内存的寿命与写操作频繁程度、存储单元最大写操作次数有关。在PCM主存中,不管DRAM作为读写Cache还是写Cache,Cache的相联度对PCM写操作次数的影响都很大,因此,实验中分别统计了8路、16路组相连下PCM写操作的次数。

图 6为PCM存储器最大写操作次数统计信息,其中以64B存储单元为单位进行统计,并将PCM直接作为内存使用时的最大写操作次数规格化为100%。另外,DRAM容量为256MB,图中PCM表示直接将PCM作为内存;RW_8way表示DRAM作为PCM读写Cache的结构,并且DRAM为8路组相连;W_16way表示DRAM作为PCM写Cache的结构,并且DRAM为16路组相连。

|

| 图 6 存储单元最大写操作次数 |

由图 6可知,不管是基于DRAM读写Cache还是基于DRAM写操作Cache的PCM主存,每64B存储单元最大写操作次数都减少了很多,如基准程序gcc,在W_16way时最大写操作次数减少最多,达到80.2%,平均值也达到了56.2%,而相对与RW_16way,W_16way最大写操作次数也有很大的降低,平均值达到了24.2%。由此可见,基于DRAM写操作Cache的PCM主存可以大大延长其寿命。

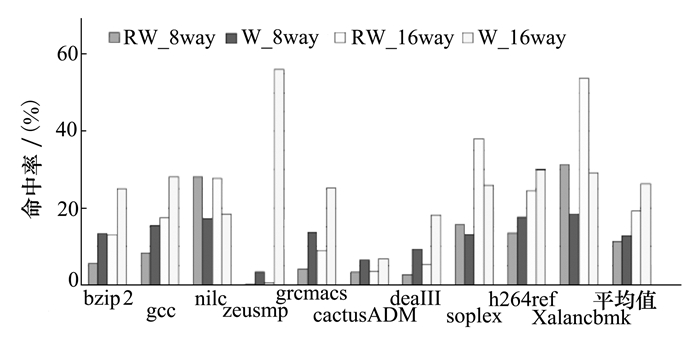

2.2.2 访存延迟分析访存延迟包括读操作延迟和写操作延迟,考虑到写操作不在关键路径上,且写操作的延迟可以通过写缓冲器来隐藏,因此文中只分析混合存储器读操作延迟。在DRAM和PCM构成的混合存储器结构中,DRAM Cache的命中率对访存性能有较大的影响,为此实验中分别统计了DRAM作为读写Cache、DRAM作为写操作Cache时读操作的Cache命中率,如图 7所示。

|

| 图 7 不同配置下读操作的Cache命中率 |

由图 7可知,基于DRAM读写Cache和基于DRAM写操作Cache的PCM主存,读操作的Cache命中率都不高,这是由于片上Cache响应了大部分读操作请求,并且片上Cache的命中率一般都比较高,因此DRAM Cache读操作的命中率较低,平均值不到40%。

在DRAM作为PCM读写Cache结构中,当读DRAM缺失后,需要串行对PCM进行读操作,此时整体读操作延迟等于两者读操作延迟之和。而在DRAM作为PCM写操作Cache的结构中,由于同时对DRAM和PCM进行读操作,因此整体读操作延迟要小于两者之和。在DRAM读写Cache结构中,DRAM命中和缺失情况下的读操作延迟分别为15 ns和37 ns;在DRAM写操作Cache结构中,DRAM命中和缺失情况下的读操作延迟分析为15 ns和22 ns。

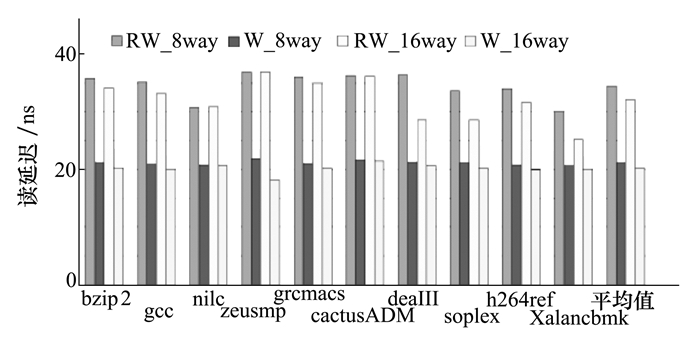

结合这2种结构中不同情况下的读操作延迟及2种结构下DRAM读操作的命中率(见图 7),可以得到2种混合存储器结构整体读操作延迟情况,结果如图 8所示。

|

| 图 8 不同配置下混合存储器读操作的延迟(ns) |

由图 8可知,与DRAM读写Cache混合存储器相比,基于DRAM写操作Cache的PCM主存的读操作延迟降低了很多,在8路组相连时,平均延迟降低了38.8%,在16路组相连时,平均延迟降低了37.1%。

3 结论本文针对PCM主存的寿命问题,提出了延长PCM主存寿命的DRAM写操作Cache结构,即DRAM Cache只缓存对内存进行写操作的数据,而对读操作则直接送往处理器核,从而减少了对PCM主存的冲击。另外,本文还提出了基于写操作频率的替换策略,减少了DRAM写操作Cache中数据的频繁换入换出。实验结果显示,本文提出的结构及调度策略能有效延长PCM主存的寿命,并提高了整体的访存性能。

| [1] | Weste H E Neil, Harries Money David. CMOS VLSI Design:A Circuits and Systems Perspective[M]. 4th Ed. Boston: Addison-Wesley , 2010 . |

| [2] | Nair J Prashant, Kim Dae-Hyun, Qureshi K Moinuddin. ArchShield:Architectural Framework for Assisting DRAM Scaling by Tolerating High Error Rates[C]//the 40th IEEE/ACM International Symposium on Computer Architecture, 2013:72-83 |

| [3] | Burr W Geoffrey, Kurdi N Bulent, Scott J Campbell, et al. Overview of Candidate Device Technologies for Storage-Class Memory[J]. IBM Journal of Research & Development , 2008, 52 (4/5) : 449–464. |

| [4] | Hay Andrew, Strauss Karin, Loh H. Gabriel, et al. Preventing PCM Banks from Seizing Too Much Power[C]//The 44th Annual IEEE/ACM International Symposium on Microarchitecture, 2011:186-195 |

| [5] | Dhiman Gaurav, Ayoub Raid, Rosing Tajana. PDRAM:A Hybrid PRAM and DRAM Main Memory System[C]//The 44th Design Automation Conference, 2009:664-669 |

| [6] | Yoon HanBin, Meza Justin, Ausavarungnirun Rachata, et al. Row Buffer Locality Aware Caching Policies for Hybrid Memories[C]//The 30th IEEE International Conference on Computer Design, 2012:337-344 |

| [7] | Qureshi K Moinuddin, Srinicasan Vijayalakshmi, Jude A Rivers. Scalable High Performance Main Memory System Using Phase-Change Memory Technology[C]//The 36th IEEE/ACM International Symposium on Computer Architecture, 2009:24-33 |

| [8] | Park Kyu Sung, Maeng Kyu Min, Park Ki-Woong, et al. Adaptive Wear-Leveling Algorithm for PRAM Main Memory with a DRAM Buffer[J]. ACM Trans on Embedded Computing Systems , 2014, 13 (5) : 1–25. |

2. AVIC Xi'an Aeronautic Computing Technique Research Institute, Xi'an 710065, China