2. 空军工程大学 防空反导学院, 陕西 西安 710051;

3. 中国人民解放军 空军93861部队, 陕西 三原 713800

LDO线性电压变换器作为电源管理芯片的一种,降低静态电流是减小LDO功耗和优化LDO指标各项性能的关键因素[1, 2, 3]。目前,大功率负载的电源管理芯片趋于把功率分立器件集成到芯片内部,使得芯片内部的功耗变得更大,特别是当输出电流过载甚至短路时,功率管上输出的大电流将会永久损害电源管理芯片和后端电阻产品。因此,过载、短路电流限制是电源管理芯片的重要研究方向[4, 5]。针对电流过载、短路问题,本文从限流的原理出发,设计了一款结构简单、低功耗的应用于线性稳压器的折返式限流保护电路,有效实现了过载电流保护及短路电流折返功能。

1 限流保护的类型 1.1 LDO线性稳压器中实现限流保护常采用的方法 1.1.1 电流比较方式此种方式通常将采样负载电流与基准电流作比较[6, 7],如图 1a)所示,利用输出信号VC控制功率管,达到限制甚至关断LDO调整管的输出电流。此种方法的静态电流随着负载的增加增大,而现代芯片要求静态功耗逐步减小以提高效率,从此点出发,该方法在一定程度上限制了其应用。

|

| 图 1 限流保护电路常用的比较方式 |

如图 1b)所示,通过采样电阻将采样负载电流转换成一个标示其大小的电压信号,用此电压与所设置的阈值作比较得到的输出结果来调节功率管的导通特性[4, 7]。由于此种方法不需要额外的基准电流,同时,采样电流比较小,为μA级,故而消耗的功率比较小。

以上2种LDO限流电路的设计通常要满足:

1) 未发生限流时,限流不影响LDO的正常输出;

2) 当限流出现时,限流保护电电路应该影响甚至取代LDO的负反馈环路;

3) 在限流消失后,能恢复到正常输出状态。

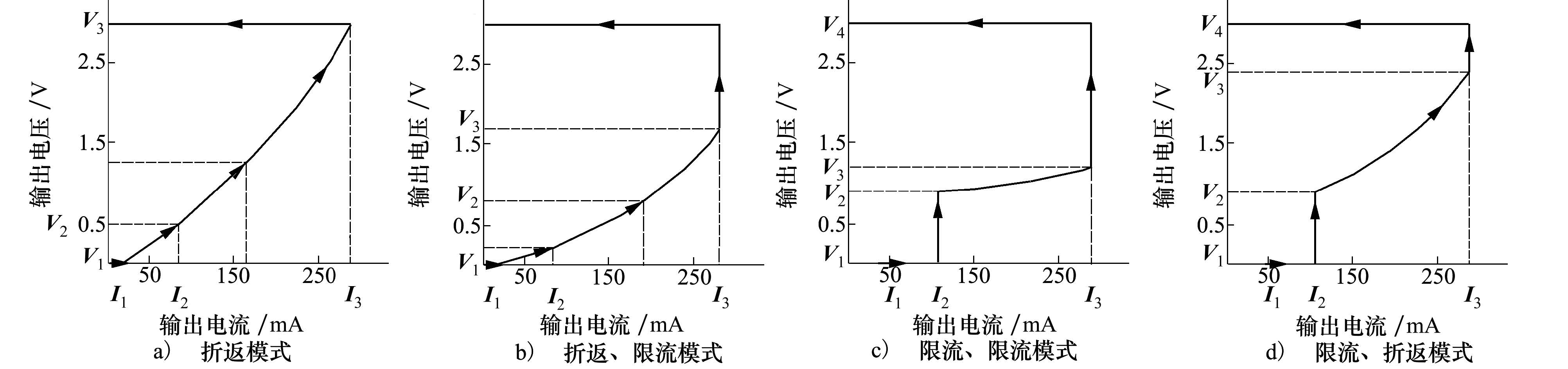

1.2 限流模式限流电流根据启动时的工作状态可以分为以下4种模式[7]:

1) 折返模式

如图 2a)所示,在芯片启动的过程中,输出电流从V1、I1开始建立,折返限流值随着输出电压的升高逐步增大,在达到设置的输出电压V3时,限流值达到最大值I3。此种方法具有实现电路简单、占用面积较小的优点,且随着折返电流精确度不高问题的解决,该限流方法在一些产品中得以应用,但在输出电压较低情况下,出现的“栓锁效应”限制了其广泛应用[8]。

|

| 图 2 限流电路的4种工作模式 |

2) 折返、限流模式

由于折返模式的精确性不足,人们提出了折返、限流模式。如图2b)所示,其启动过程与折返模式启动过程类似,但当输出电压达到设定的值V3后,输出电流以I3输出。限流、折返电路与折返电路一样具有实现电路简单、功耗低、面积小的优点,但同样也有栓锁效应的缺陷。

3) 限流、限流模式

为克服模式1、2的缺陷,出现了限流、限流模式。如图2c)所示,在上电的过程中,在Vout低于设定值V2的情况下,调整管以值I2输出电流,随着输出电压的升高,到达V3时,限流值切换到I3,即以I3值输出。虽然克服了启动误判的问题,却导致新问题的出现:当输出电压出处在V3~V4之间时,输出电流依然维持在I3,使得功耗损失较大。

4) 限流、折返模式

如图2d)所示,折返、限流模式克服了以上几种模式的缺点,能够较好实现折返、限流功能,但功耗、复杂程度、占用面积上大大超过了模式1、2及3。

鉴于以上模式的优缺点,本文所提出的限流电路采用电压比较方式的限流、限流模式,此种模式较好克服了模式1、2启动过程中的缺陷,并且较模式4而言,具有电路简单、功耗低、占用面积非常小的优点。

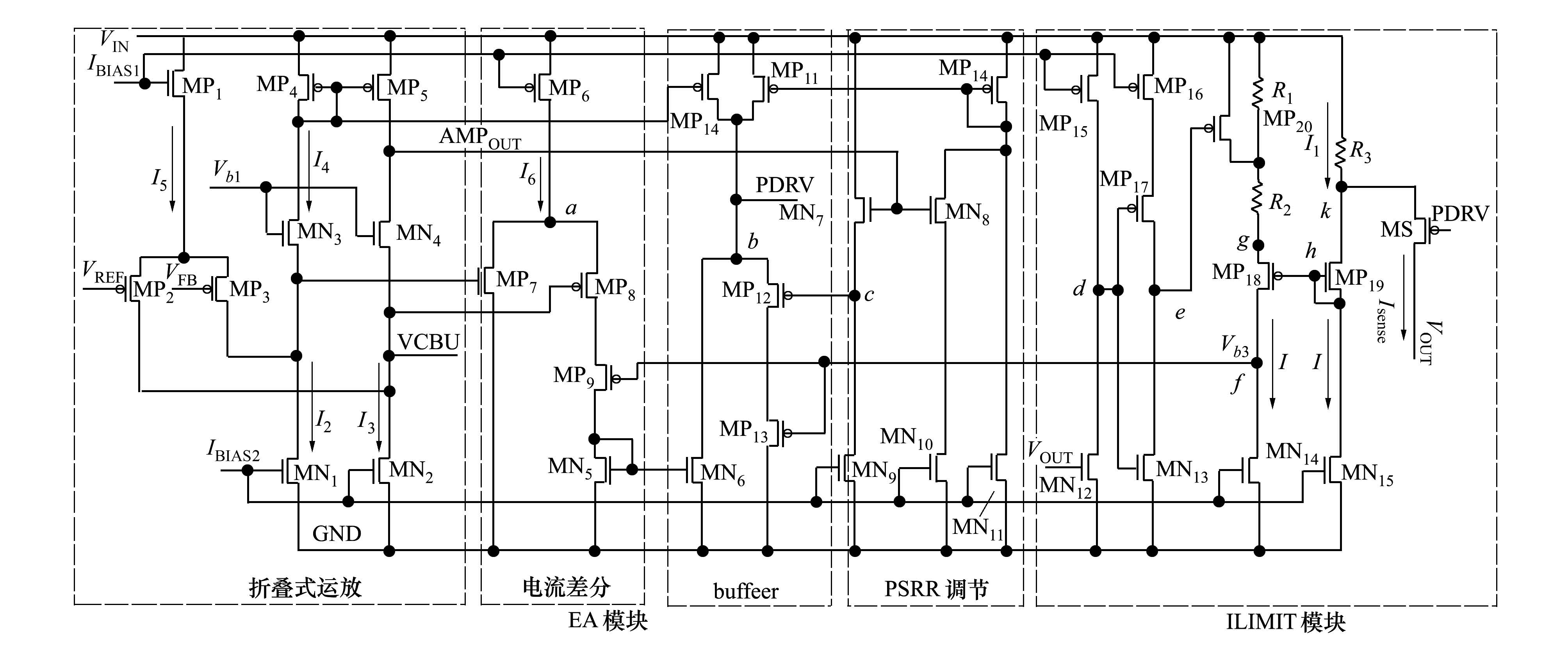

2 本文提出的限流电路架构图 2.1 原理分析如图 3所示,电路由EA模块及ILIMIT模块组成,其中EA模块包括:折叠式运放、电流差分、buffer、PSRR调节部分及VCBU环路补偿端口[9]。运放对电压信号VREF、VFB进行差分放大,然后,经buffer中MN6、MP13支路实现对功率管驱动电压(PDRV)的调节:① 动态调整MP7、MP8的gate端电压,实现对MP8支路中电流的动态调节,通过MN6对MN5的镜像作用形成第一部分下拉电流;② 运放的输出端AMPOUT作用于MN7、MN8,动态调整c点电压,使得流经MP12、MP13的电流构成第二部分下拉电流。两支路在限流功能中的作用会在限流、短路折返过程中阐述。其中电流差分、PSRR调节部分可以实现所设计的LDO的高PSRR作用,由于重点在ILIMIT,此功能在此处不作详述。

|

| 图 3 EA_ILIMIT架构图 |

VB3为限流部分输出信号,输入到EA模块的电流差分及buffer部分,它随着输出电流的增加而增加。若输出电流在正常带载范围内,VB3信号不影响输出电流。但输出电流超出最大负载后,限流控制信号逐步减弱甚至消除环路的负反馈作用,即:VB3改变MP9、MP13的导通特性,从而实现对下拉电流的控制,进而实现对PDRV的控制,最终实现限流功能。具体分析计算如下:

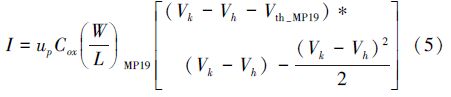

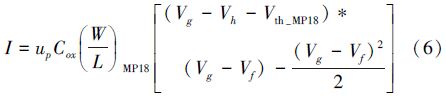

设单位电流为I,采样电流为Isense,因此可得流经采样电阻R3上的值:

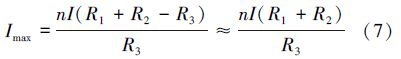

当Vg=Vk时,由公式(1)~(4)可得最大输出电流Imax为

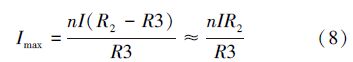

由(7)可知,在给定的偏置电流为I的情况下,限流值Imax与R1、R2成正比,与R3值成反比。当输出负载的减小,输出电流趋于增大,EA的折叠运放的反馈作用趋于使得流经MP8电流增大即:Rload↓→Vout↓→VFB↓→Vgate_MP8↓→IMP8↑→IMP6↑→PDRV↓→Iout↑→Vout↑(注:↑表示上升,↓表示下降)。与EA的反馈作用相反,VB3电压随着Iout的增加而增加,趋于使得MP8中电流减小,逐步削弱EA的负反馈调节作用,最终使输出电流不超过Imax。输出电流达到限流值后维持不变,输出电压Vout随着负载电阻的减小而减小,当VoutVth-MN12时,MN12关断,d点电压被拉为高电平,经过电流源反相器e点电平输出为低,开关管MP20导通,屏蔽掉R1,此时,最大输出电流变为短路折返电流Ifoldback,相应的公式(7)可改写为

从公式(7)、(8)可以看出,通过调节R1、R2的大小可以调节Ifoldback的大小,即控制Ifoldback与Imax的比例关系。

2.2 不同输入电源电压情况下Imax的实现过程随着输出电流的增大,EA的负反馈作用逐步减弱,ILIMIT限流环路的负反馈作用逐步加强,达到限流值后,前者被后者完全取代。本文中提出的限流环路利用buffer双支路(即MN6、MP13支路)实现,其工作状态随输入电压有所转变,具体分析如下:

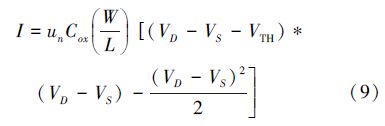

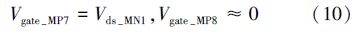

MN6支路偏置电流随输入电源电压变化,为实现限流值的稳定,利用MP13支路进行互补;输出电流达到限流值后维持不变,输出电压随着负载电阻的减小而减小,随着负载电阻的进一步减小使MP1的偏置电流I5=I6全部流过MP3管,易得I3=I4=I2-I5=I2-6I=10I-6I=4I,即流经MN1、MN2管的电流不再发生改变,为常值。通常,MOS管子流过的电流与电压的关系为:

由公式(9)可得:

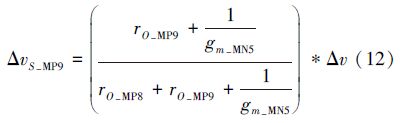

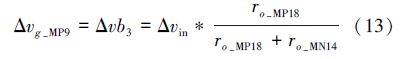

由公式(9)、(10)可知,MP7、MP8的gate端电位在不同的输入电压下基本保持不变。设输入电源电压的增加量为Δvin,MP7、MP8的跨导分别为:gm_MP7,gm_MP8,MP8、MP9的导通阻抗为ro_MP8,ro_MP9。由于MP6的沟道调制效应,a点随输入电源增加量为Δv,其中Δvin$ \gg $Δv。则根据小信号分析可得:

公式(15)显示,MP7管的电流随着输入电源电压增大逐步增大,MP8管的电流随着输入电源电压增大逐步减小,导致镜像入MN6管的电流逐步减小,下拉作用减小,使得限流值在不同的电源电压下变动较大。为改善这一缺陷,增加了由MP12、MP13组成的第2路下拉偏置电流支路。

一般情况下,MN6、MP13支路均有电流流过,由此2条反馈构成环路共同作用将限流值稳定在Imax。在电源电压较高或较低极端情况下,此2支路构成的限流环路的转换过程为:在电源电压较低时,由MP12、MP13组成的支路正常工作需要Vmin_PDRV=VB3+VTH_MP13+VDS_MP12,由于PDRV电压较低,该支路无法正常工作。由MP7、MP8、MP9、MN5、MN6、PDRV、VB3、Iout、MP18及MP19构成反馈环路,使得限流电流维持在Imax,即:Iout↑→VB3↑→IMP5↓→IMP6↓→PDRV↑→Iout↓,反之,Iout↓→VB3↓→IMP5↑→IMP6↑→PDRV↓→Iout↑。随着输入电源的增加,MN6管的电流逐步减小,其反馈调节逐步减弱,由MP13、VB3、PDRV、Iout、MP18、MP19构成的负反馈环路作用逐步增强,当MN6中无电流流过时,则:

环路中的限流值仅由此支路构成的环路决定,使其维持在Imax,其负反馈作用为: Iout↑→VB3↑→ro_MP13↑→PDRV↑→Iout↓,反之,Iout↓→VB3↓→ro_MP13↓→PDRV↓→Iout↑。

在折返限流情况下,MN6、MN13在高、低电源下的工作状态与在常值限流情况下的工作状态相同,不再赘述。

由于限流部分的静态偏置电流I的值为460 nA,且设置MP15尺寸为W=1 μm,L=100 μm,MN12尺寸为W=5 μm,L=1 μm,以保证正常工作情况下d点维持低电平,且减小该部分工作时的静态功耗。由于反相器不消耗电流,限流部分的静态电流为2 μA,在面积允许情况下通过增大R1、R2的值可进一步减小静态电流到1 μA。

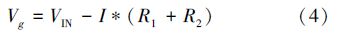

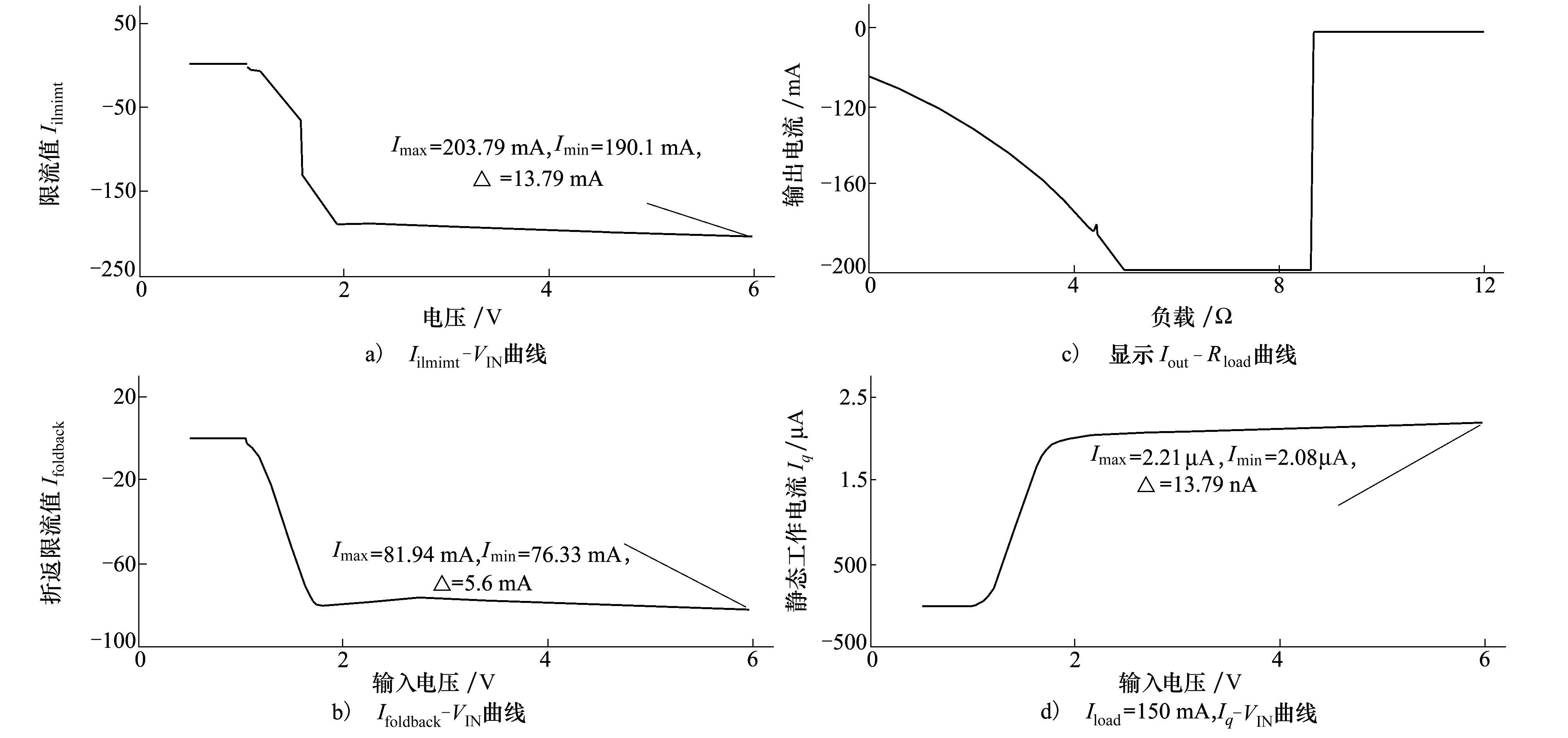

3 仿真验证采用HJ 0.5 μm 5V COMS Process,借助candance hspices工具对提出的折返式限流电路进行仿真。仿真结果包含Iilmimt-VIN曲线、Ifoldback-VIN曲线、Iout-Rload曲线及ilimit模块的Iq-VIN曲线。图 4a)为Iilmimt-VIN曲线,从图中可以看出,在输入电压从2.3~6V范围内,Iilmimt限流值变化13.79 mA,能够实现最大带载150 mA情况下的限流功能;图 4b)中Ifoldback-VIN曲线显示,在输出端判断为短路后,Ifoldback降低到大约80 mA,在输入电压从2.3 V上升到6 V,该值变化量为5.6 mA,成功实现短路情况下折返限流的作用;图 4c)显示Iout-Rload曲线,其中Rload在10 ms范围内由18 Ω减小到0.1 Ω,输出电流结果显示,电路成功实现限流(203.9 mA)、折返限流(81.83 mA)功能;图 4d)显示,在带载150 mA情况下,Iq-VIN曲线,最大静态功耗2.08 μA,在面积允许的情况下,可以通过增大R1、R2的值进一步减小静态电流到1 μA。

|

| 图 4 折返式限流电路仿真结果 |

本文成功设计了一种结构简单应用于低压差线性稳压器的限流保护电路,实现了限流200 mA、折返限流80 mA的功能,同时自身消耗静态电流很小。仿真验证表明限流值稳定,输出电流基本不随着电源电压变化而改变,起到了保护电路的作用。

| [1] | Bontempo G, Signorelli T, Pulvirenti F. Low Supply Voltage, Low Quiescent Current, ULDO Linear Regulator[C]//IEEE International Conference on Electronics, Circuits and Systems, 2001: 409-412 |

| Click to display the text | |

| [2] | Sai Kitlau, Ka Nangleung, Philip K T Mok. Anaysis of Low-Dropout Regulator Topologies for Low-Voltage Regulation[C]//IEEE International Conference on Electron Devices and Solid State Circuits, 2003: 379-382 |

| Click to display the text | |

| [3] | Li Yanming, Lai Xinquan, Jia Xinzhang, et al. A Fast Transient Response and Low-Quiescent Current CMOS Low-Dropout Regulator[J]. Acta Electronica Sinica, 2009, 37(5):1130 |

| Click to display the text | |

| [4] | Guo Jianping, Ka Nang Leung. A Fold-Back Current-Limit Circuit with Load-Insensitive Quiescent Current for CMOS Low Dropout Regulator[C]//IEEE International Symposium on Circuits and Systems, 2009: 2417-2420 |

| Click to display the text | |

| [5] | Lin Chuan, Feng Quanyuan. Design of Current Limiting Circuit in Low Dropout Linear Voltage Regulator[C]//IEEE AMPC2005 Proceedings, 2005 |

| Click to display the text | |

| [6] | Li Yanming, Mao Xiangyu, Wang Hongyi, et al. An Improved Hiccup Mode Short-Circuit Protection Technique with Effective Overshoot Suppression for DC-DC Converters[J]. IEEE Trans on Power Electronics, 2013, 28(2): 877-885 |

| Click to display the text | |

| [7] | Cheng X J, Wu X. A High-Performance Foldback Current Limiting Circuit for Improving Regulators' Latch-up Effect[C]//IEEE International Conference on Communications on Circuits and Systems Proceedings, 2006, 30: 2248-2250 |

| Click to display the text | |

| [8] | Qian Min. Study on the Mechanism of Latch-Up Effect in CMOS IC and Its Countermeasures[J]. Journal of Suzhou University, 2013, 19: 31-38 |

| Click to display the text |

2. Key Lab of High-Speed Circuit Design and EMC, Ministry of Education, Xidian University, Xi'an 710071, China;

3. PLA, No.93861 Troop, Sanyuan 713800, China