2. 西北工业大学 计算机学院, 陕西 西安 710072;

3. 中国航天科技集团公司科技委, 北京 100048

空间辐射环境中的粒子,会导致运行于轨道上的卫星、飞船等航天器电子系统中的VLSI半导体器件发生单粒子效应,严重影响航天器的可靠性和寿命[1]。

可将单粒子效应故障分为硬错误和软错误2大类。硬错误表现为器件本身永久性的损坏,如SEB、SEGR、SPDD、SHE等。软错误则表现为电路逻辑状态的翻转、存储数据的随机改变,而器件本身没有损坏,但如果再次写入相同的数据,错误可能会在其他位置出现,如SET、SEU、MBU、SEFI等[2]。空间环境中的单粒子翻转效应是一种常见的单粒子效应软错误。

当前,比较常用的检查和纠正单粒子翻转的方法有三模冗余(TMR)法和检测/纠正电路等。三模冗余是把要保护的电路复制成完全相同的3份,同时运行这3部分电路,并且对该3部分电路的运行结果进行大数表决,把表决出的一个置信度高的结果输出,同时指出哪个逻辑块翻转并进行修复。TMR是解决SEU影响的最有效方式,但需要消耗大量的资源才能实现该电路结构。检测/纠正电路则是采用如海明码等不同的编解码方式,在存储的数据源码中加入一些冗余码,使这些数据源码和冗余码之间建立一定的关系,一旦数据源码或冗余码出现某种错误时,数据码和冗余码之间的关系被破坏,就形成非法编码,通过检测数据码和冗余码来检测数据码的正确性,能实现对所存储数据进行检测和纠正[3]。

近年来,有研究人员[3, 4]提出了一种基于时钟沿的单粒子翻转检测纠错电路。本文参考其思想,设计了一种改进的基于时钟沿的单粒子翻转自检纠错电路结构,该电路在保持原有电路优点的同时,克服了循环(震荡)不已、不能收敛的不足;此外,在进行简单扩展后,能完成上升沿或下跳沿错误检测,并可以同时实现多位SEU错误检测纠正。

1 时钟沿检测和纠错电路原理基于时钟沿的检测和纠正电路的基本原理是[4],“对于触发器,输出数据只有在时钟上升沿到来时发生转变,才是有效的正确数据,而其他任何时刻的变化都是由于单粒子软错误引起的信号错误”。据此,基于时钟沿的检测和纠正电路,可以通过对比数据与时钟的转变沿是否同步,来实现数据的检测和纠正。

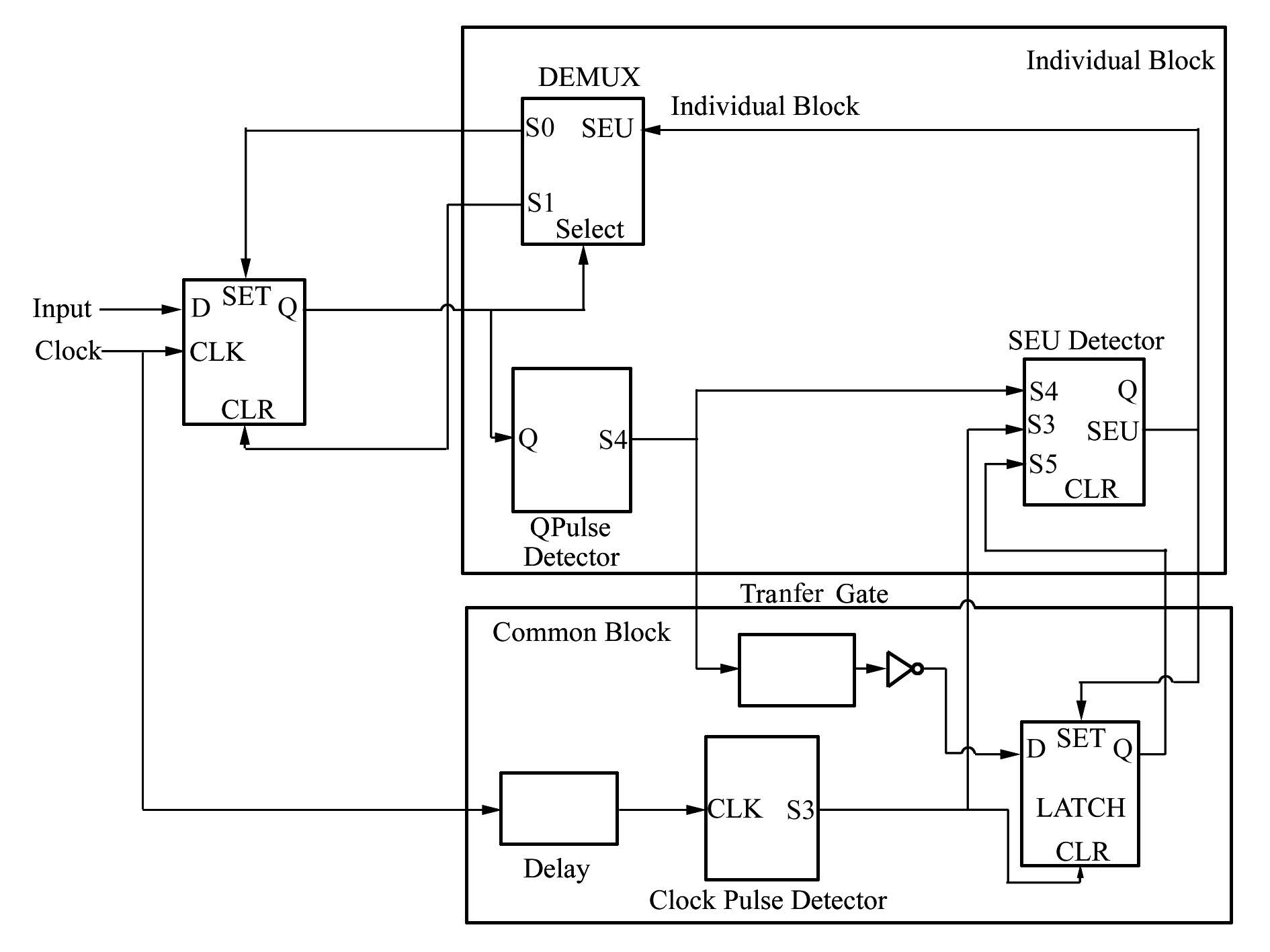

参考文献[3]中的电路结构如图 1所示。

图 1的工作原理可简述如下:

比较单元的核心部分可由如下表达式表述为 SEU-O=Data-pulse×Clk-pulse。式中,Data-pulse是数据信号经过沿检测电路后的信号,Clk-pulse是时钟信号经过沿检测电路后的信号。在时钟处于上升沿时,Clk-pulse会产生一个正向脉冲,如果此时数据发生翻转,Data_pulse也会产生一个正相脉冲,因此SEU-O将保持0不变;当受SEU影响,使数据发生翻转时,Data-pulse会产生一个脉冲,而此时由于不是在时钟上升沿,信号Clk-pulse将保持为1,故输出信号SEU-O就被置为1。由此,当没有SEU错误发生时,SEU-O为0;当发生SEU错误时,SEU-O为1。

错误纠正电路的核心是运用一个多路输出选择器来纠正触发器的错误输出信号。多路输出选择器的输入信号为SEU-O,输出选择信号为触发器的输出信号,2个输出信号分别连接到触发器的复位端和清零端。

由以上的分析可知,检测到有错误发生时,SEU-O的值为1。此时,如果Q值为1(正确值应该为0),那么就把SEU-O的值1赋给S1,且触发器被清零,Q被置为0;如果Q值为0(正确值应该为1),则把SEU-O的值1赋给S0,且触发器被置为1,Q被置为1,从而实现对Q值的纠正;如果没有错误发生时,SEU-O的值为0,此时不论触发器的输出信号Q为1或0,都不会对Q值产生影响。

为了避免检测电路把纠正之后的Q值作为SEU而引起的错误值来进行处理和纠正,图 1所示的电路添加了一个触发器,用以锁存以前的电路状态。信号SEU-O与信号S3、S4、S5有关,可以表示为SEU-O=S4×S3×S5。

由此,每一个时钟上升沿到来时,就会对触发器清零,电路可以对数据进行检测和纠正。若在1个时钟周期内,第1次发生单粒子翻转,并检测到SEU-O由0变为1,同时触发器被置为1,进而SEU-O的值又变为0,纠正后的数据产生数据沿脉冲不会对SEU-O的值产生影响,从而完成这一次的数据检测和纠正。

2 改进的时钟沿检测和纠错电路 2.1 电路结构图 1所示方案,虽然能以较小的面积和使用较少的逻辑器件来实现单粒子翻转的检测和纠正,但是它存在2个问题:①对于数据转变沿的检测,只可以检测0到1的转变,不能检测到1到0的转变,因而对由于SEU引起的由1变为0的数据错误翻转无法检测,影响电路系统的稳定行;②当一个时钟上升沿来临,锁存器的输出Q被清零,SEU-O的值只与数据沿和时钟沿有关。当任何一个触发器的输出由于受到SEU的影响而发生翻转时,通过各个独立模块的错误检测电路,会检测出有错误发生。此时,该独立模块的SEU-O变为1,并对该模块中的触发器输出进行纠正。同时,公共模块的锁存器被置为1,SEU-O变为0,并且与S3和S4无关,直到下1个时钟上升沿到来时,锁存器才被再次置为0,才会随着S3和S4发生变化。因此,该电路结构在1个时钟周期内,只能检测和纠正1次单粒子翻转引起的数据输出错误。若在只有一位触发器的情况下,电路在每一个时钟最多发生1次翻转的假设是可以接受的。但是,随着电路规模和功能要求的增加,这将限制电路对数据错误的检测和纠正,从而严重影响电路系统的可靠性和实用性。

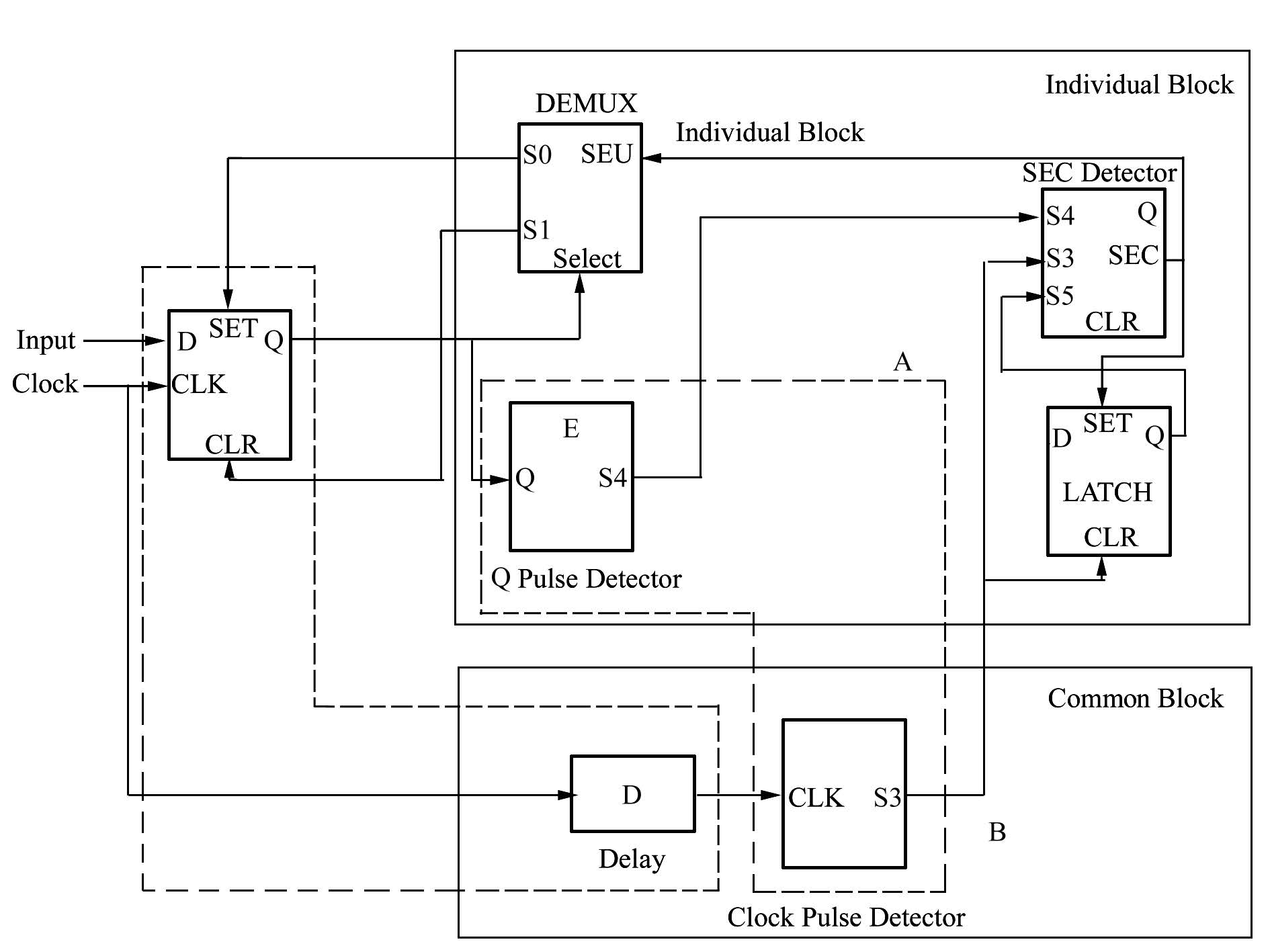

此外,图 1所示的组合中存在回路,由电路仿真可知,该组合电路可能会导致电路死循环(震荡),而不能收敛。为此,本文下面设计了一种改进的电路结构,以克服上述电路的不足。改进的时钟沿检测和纠错电路结构如图 2所示。

|

| 图 2 改进的时钟沿检测和纠错电路结构 |

图 2所示的电路结构由两部分组成,A框内是每一个数据单独具有的错误检测和纠错部分;B框内是该电路的公用部分。D模块采用和C模块相同的电路结构进行设计,以保证两者电路延迟相同。此外,为保证C模块与D模块,以及E模块与F模块,在线延迟上保持一致,在设计时采用如下策略:

1)将C模块和D模块、E模块与F模块分别作为一个整体进行设计;

2)在布线时对器件添加区域约束,使C模块和D模块间的距离,以及E模块与F模块间的距离尽量接近。

图 2所示电路主要组成模块的结构和功能描述如下:

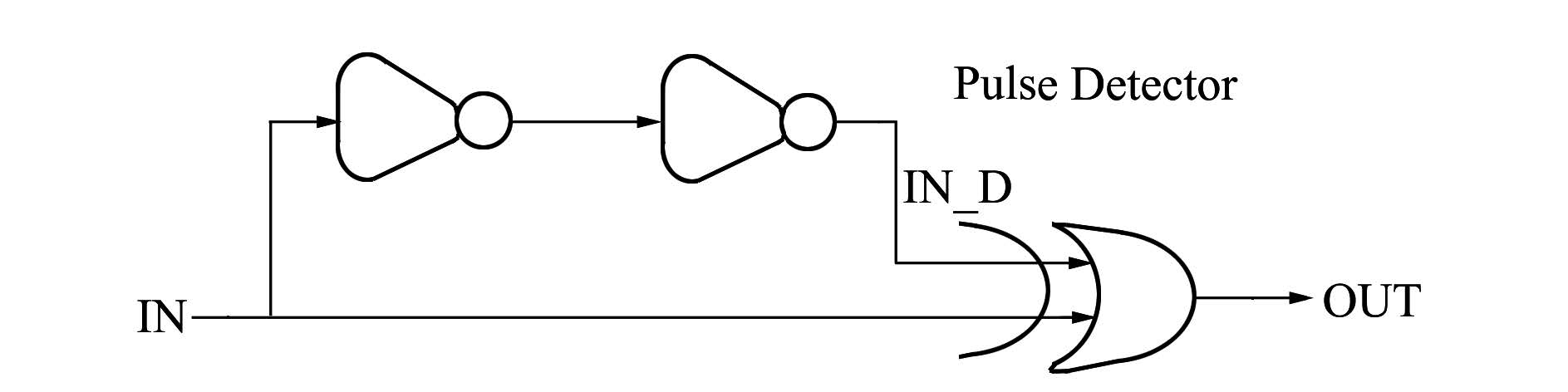

1)Pulse Detector模块

输入信号IN经过2级非门产生信号IN-D(主要作用是对输入信号进行延迟),再将IN-D与信号IN进行异或操作,得到输出信号OUT。Q Pulse Detector采用图 3所示结构。

|

| 图 3 Q Pulse Detector结构 |

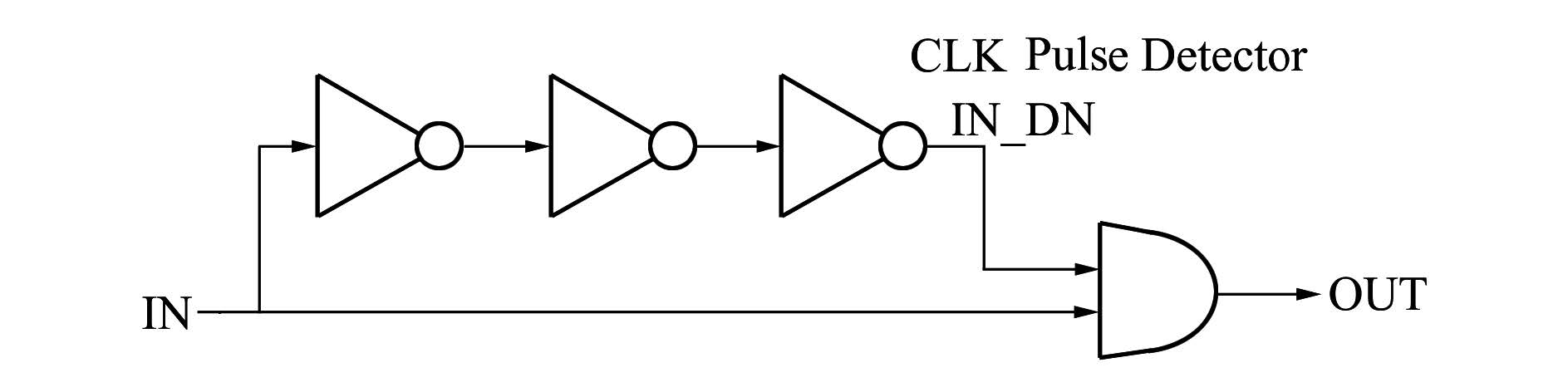

2)CLK Pulse Detector模块

若原始电路在时钟上跳沿和下降沿均发生数据输出,则CLK Pulse Detector模块采用与Pulse Detector模块相同的电路结构。若仅仅在上跳沿完成检测,则CLK Pulse Detector模块采用图 4所示结构。

|

| 图 4 CLK Pulse Detector结构(上升沿的正确检测电路) |

在图 4的结构中,也可以采用奇数个非门,这里采用3个非门主要是为增加脉冲的宽度。若仅在下降沿完成检测,则在采用图 4所示结构的IN端增加1个非门即可。

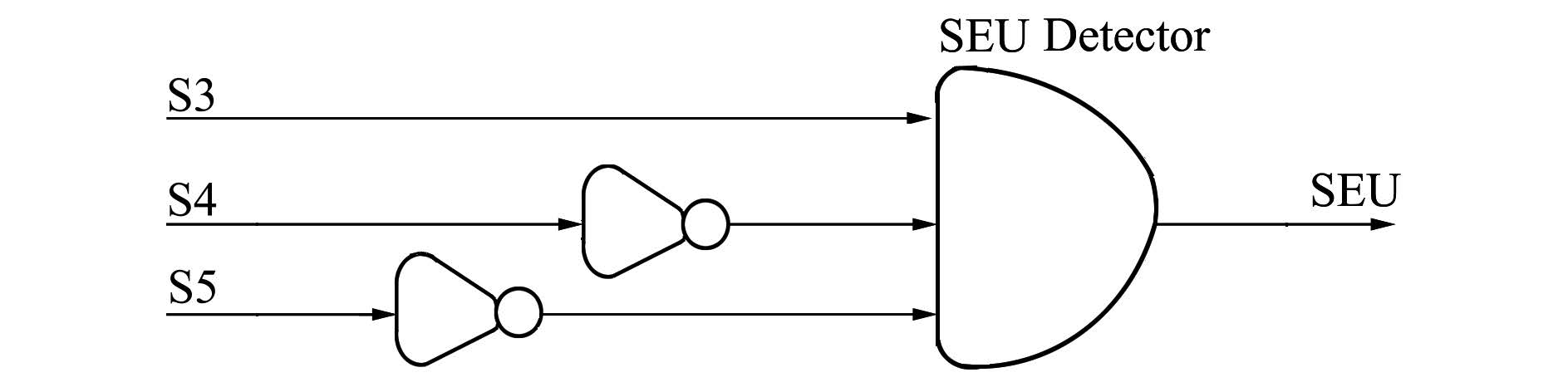

3)SEU Detector模块

SEU Detector模块的结构如图 5所示。它将“输入信号S3”、“输入信号S4的非”和“输入信号S5的非”进行与操作,产生输出信号SEU。

|

| 图 5 SEU Detector结构 |

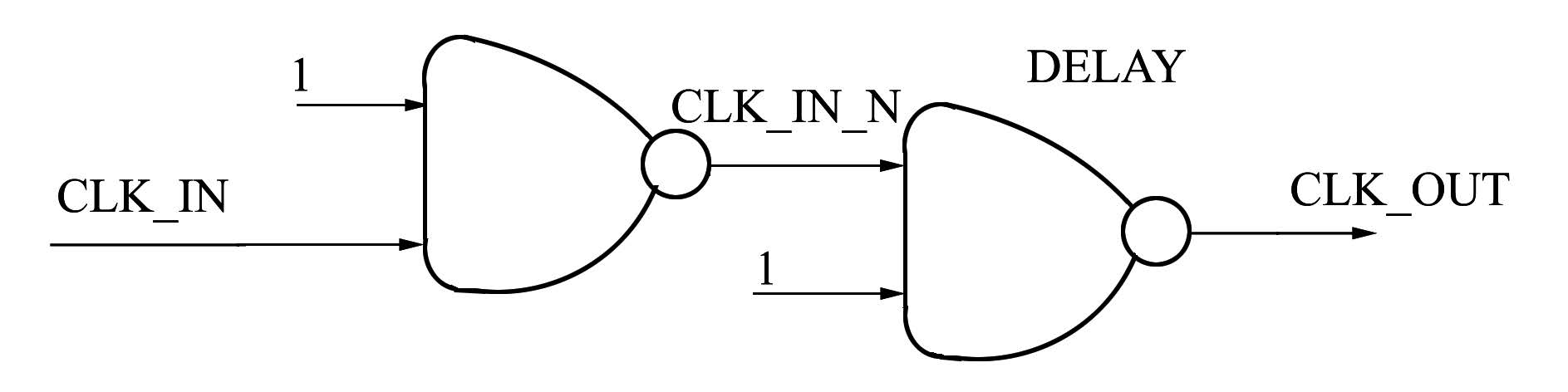

4)Delay模块

Delay模块结构如图 6所示。将输入信号CLK-IN与1进行与非操作,产生CLK-IN-N;再与1进行与非操作,产生输出信号CLK-OUT。

|

| 图 6 Delay模块结构 |

5)Demux模块

Demux模块(多路输出选择器)的输入信号为SEU,输出信号为S0、S1,分别连接触发器的置位端和清零端。

如果没有错误发生时,SEU的值为0,此时不论触发器的输出信号Q为1或0,S0、S1均输出0,不会对Q值产生影响;而当有错误发生时,SEU的值为1,如果Q值为1(正确值应当为0),则S1输出1,触发器被清零,Q被纠正为0;如果Q值为0(正确值应该为1),则S0输出1,触发器被置1,Q被纠正为1,从而实现SEU错误的纠正。

Latch模块和触发器模块分别与标准的锁存器的功能和结构以及标准的触发器的功能和结构相同。

2.2 工作原理图 2的电路结构采用2个非门和1个异或门。利用2个非门来产生延时,异或门对延时后的信号和原来的信号进行比较,进而在上升沿和下降沿时产生一个脉冲,用于数据沿的检测。同时,该电路添加了逻辑电路,以实现对由SEU引起的错误数据的多次检测和纠正。即在公共模块上增加了1个非门和1个CMOS传输门,用于检测数据修改是否完成,并对锁存器赋值,使电路在数据纠正完成以后,让锁存器输出变为0,即恢复到没有检测到错误发生的状态。该电路可以对下一个由SEU引起的数据翻转进行检测和纠正,进而大大提高电路的稳定性和可靠性。

图 2电路的原理是,当时钟处于上升沿时,信号S3产生1个高脉冲,此时锁存器被清零。锁存器输出0时,CMOS传输门被关闭,不传输数据。当检测到由于SEU引起的Q值翻转时,SEU-O变为1,此时锁存器被置为1。当SEU-O变为1时,对数据Q进行纠正,Q值发生翻转,会产生1个高脉冲。当锁存器被置为1时,CMOS传输门导通,SEU-O又变为0。数据Q被纠正,发生翻转产生1个高脉冲,此时CMOS传输门被导通。数据Q产生的脉冲经过传输门和非门,变为低脉冲,该脉冲传输到锁存器的输入端,进而锁存器的输出变为0。此时,CMOS传输门关闭,信号SEU-O只与S4和S3有关,电路的错误检测和纠正电路恢复到没有发生错误时的状态,准备检测下一个数据沿。

该电路为2个部分,上虚框内是每一个数据单独具有的错误检测和修改部分;下虚框内是该电路的公用部分。同时,同一个时钟周期内,若将多个Individual Block设置到原始功能电路中,则可以检测和纠正多位SEU错误。

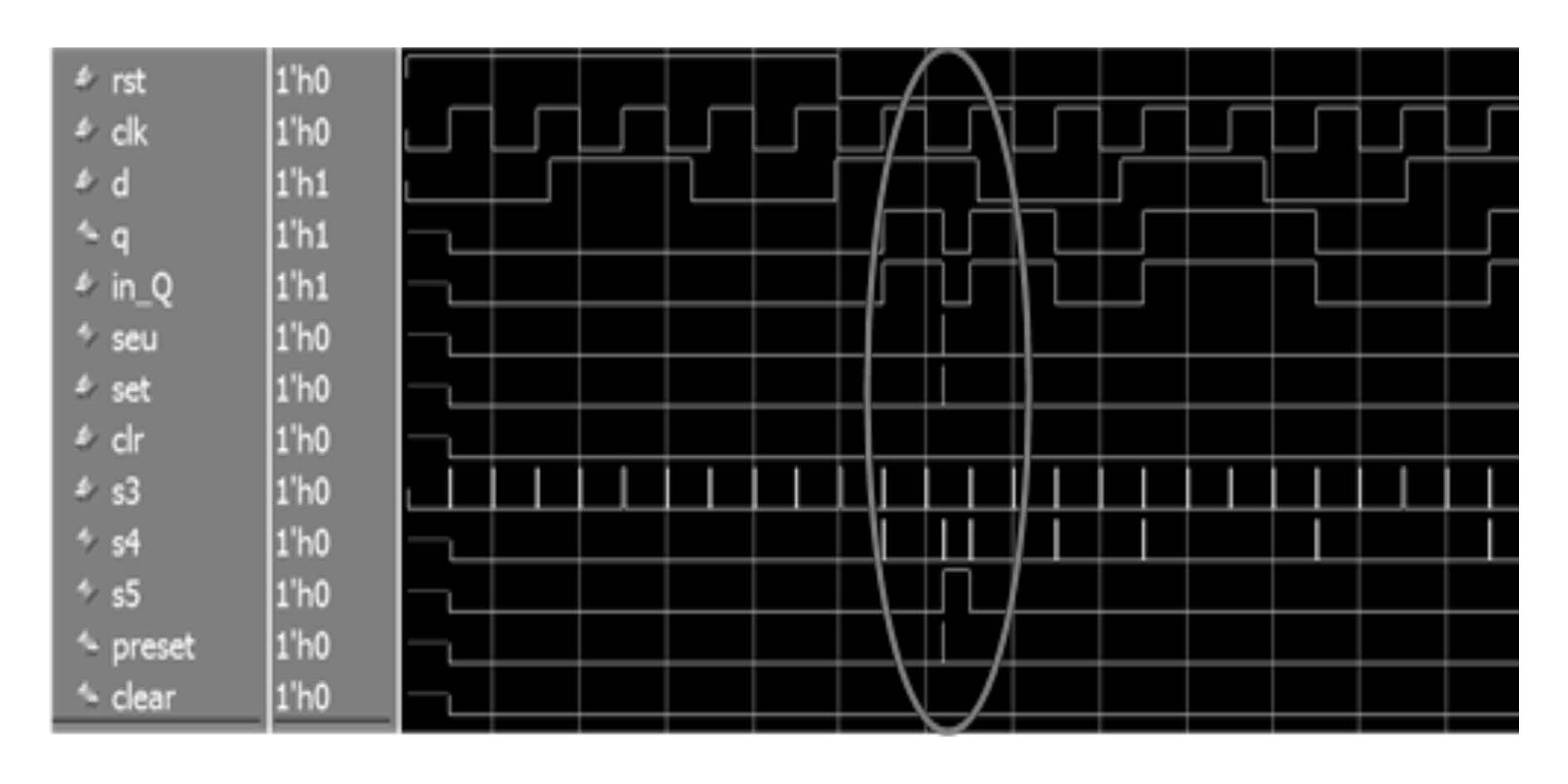

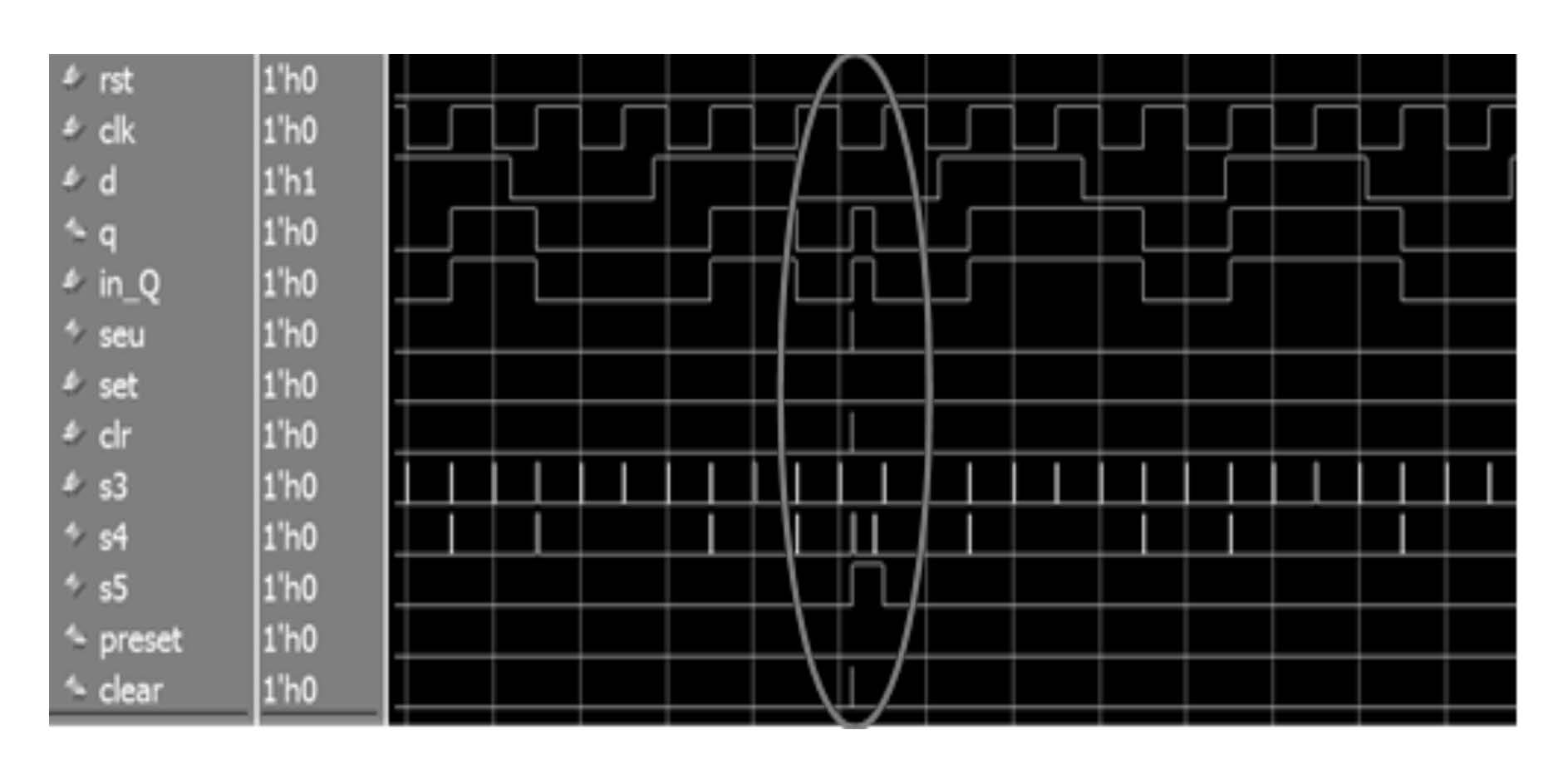

3 仿真分析本文对所提出的改进电路在Modelsim下进行了仿真[5],结果如图 7、图 8所示。

|

| 图 7 检测及纠错仿真结果(SEU导致DFF Q端1变0) |

|

| 图 8 检测及纠错仿真结果(SEU导致DFF Q端0变1) |

在仿真中,例化了2个Individual Block,并在TB中分别注入了非CLK沿的数据翻转(即SEU)。信号注入采用Force方式,由图中SET、CLR信号可以看出,纠错电路以产生相应的反应,在实际中(TB中的Force语句不起作用时,Q能够通过SET、CLR对SEU产生的错误进行纠正)。由图 7、图 8可以看出,本文设计的改进电路能很好地完成数据单粒子软错误的检错纠错。

4 结 论本文所提出的电路结构,可以对SEU引起的数据错误翻转进行有效的检测和纠正,完善了参考文献所述电路结构,在保留其优点的前提下,克服了存在的不足。此外,在提高系统抗单粒子翻转的检测和纠正能力的同时,所增加的电路结构只需消耗极少的资源。仿真和实际应用均表明,本文所提出的改进电路是一个有实用价值的检错纠错电路。

| [1] | 丁义刚. 空间辐射环境单粒子效应研究[J]. 航天器环境工程, 2007, 24(5):283-290 Deng Yigang. Single Event Effects in Space Radiation Environment[J]. Spacecraft Environment Engineering, 2007, 24(5):283-290 (in Chinese) |

| Cited By in Cnki (46) | Click to display the text | |

| [2] | 邢克飞. 星载信号处理平台单粒子效应检测与加固技术研究[D]. 长沙:国防科技大学,2007 Xing Kefei. Single Event Effect Detection and Mitigation Techniques for Space Borne Signal Processing Platform[D]. Changsha:National University of Defense Technology,2007 (in Chinese) |

| Cited By in Cnki (30) | |

| [3] | 聂永锋,于东英,曾泽嵘,甘智勇,陈梦远. 一种改进的对抗软错误电路结构设计[J]. 现代电子技术,2011,34(4):184-187 Nie Yongfeng, Yu Dongying, Zeng Zerong, Gan Zhiyuan, Chen Mengyuan. Design of EDAC Circuit Structure Depending on Clock Edge[J]. Modern Electronics Technique, 2011,34(4):184-187 (in Chinese) |

| Cited By in Cnki (1) | Click to display the text | |

| [4] | Ruano O, Reviriego P, Maestro J A. A New EDAC Technique against Soft Errors Based on Pulse Detectors[C]//The Proceedings of IEEE International Symposium on Industrial Eletronics, 2009:2293-2298 |

| Click to display the text | |

| [5] | 任向隆,马捷中,曾宪炼. 基于VHDL的故障注入技术研究[J]. 测控技术,2009,28(11):73-76 Ren Xianglong, Ma Jiezhong, Zeng Xianlian. Research on VHDL-Based Fault Injection Technology[J]. Measurement & Control Technology, 2009,28(11):73-76 (in Chinese) |

| Cited By in Cnki (7) | Click to display the text |

2. Department of Computer Science and Engering, Northwestern Polytechnical University, Xi'an 710072, China;

3. The Science and Technology Committee, China Aerospace Science and Technology Corp., Beijing 100048, China