2. 西北工业大学软件与微电子学院, 陕西 西安 710072

随着对嵌入式计算需求不断提高, 嵌入式系统的规模也越来越大, 由原来的单板单核到目前的多机多核框架。因此, 在改进其硬件设备的同时, 也需要注重软件的优化。硬件改进可以通过用高速串行rapidIO总线替换低速以太网进行板级通信, 同时采用MPI并行方式进行计算处理, 以提高系统的实时性[1]。

目前, RapidIO网络通信都需要借助以太网模拟器才能完成, 上层MPI层在使用该网络时, 需要通过socket接口, 效率非常低[2]。为了提高嵌入式系统的计算能力, 本文提出了基于SRIO总线的高性能嵌入式并行处理模型(HPEPPM)。该模型通过SRI(serial rapidIO interface)与总线交互, 其设计主要参考了流控制传输协议SCTP (stream control transmission protocol), 即通信数据都以消息的形式传输, 且支持消息的拆分和重组, 以及消息的捆绑传输[3]。为了支持SRI接口, 需要根据SRIO总线的特点, 在处理层添加MPI的调用函数, 完成与上层应用的对接, 并通过实验进行性能比对。实验结果表明, 该模型通过借助SRIO总线高速的特性, 实现底层板对板的通信, 降低了通信延迟, 提高了传输效率; 同时采用MPI的方式将多个节点资源进行高层封装, 能实现多机并行处理, 有效提高系统实时性。

1 总体结构模型在传统的多核系统或多处理器系统中, 每个处理器都具有相同的结构, 系统将任务均衡负载至各处理器中[4]。但在处理器异构平台下, 由于处理器(核)的结构差异, 导致其在任务处理中性能也各不相同。因此, 在进行异构处理器(核)平台计算时, 上层的应用需根据底层结构有所调整。

传统的基于MPI(message passing interface)架构的并行程序通常体现在进程级或任务级[5]。即将一个并行任务划分为N个子任务, 并均匀分布在各个核内运行, 再通过汇总完成整个任务的执行[6]。但在异构平台上, 均匀分布或是随机分布并行子任务显然都是不科学的。

|

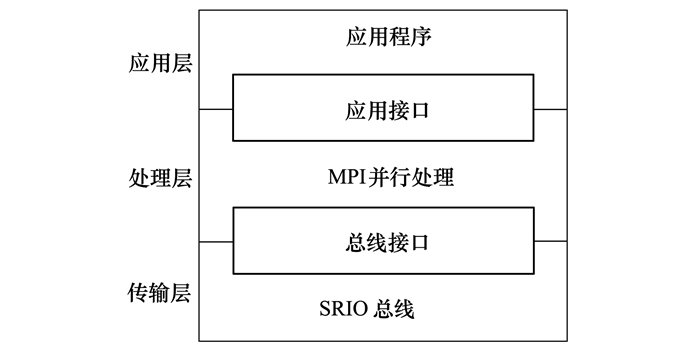

| 图 1 高速并行处理模型架构 |

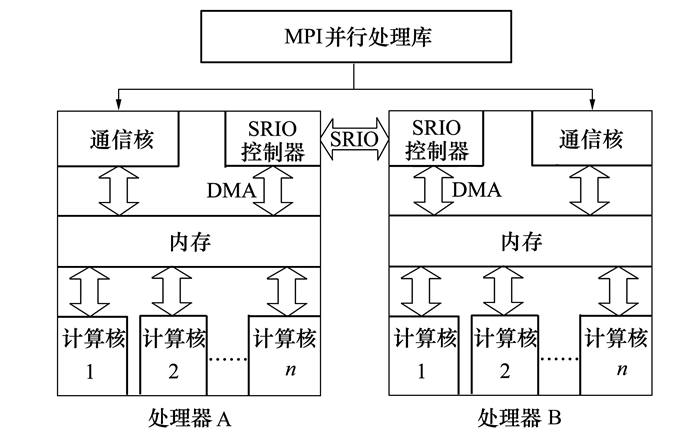

在MPI架构中, 计算任务和通信任务是相互独立的, 与异构平台中多处理器(核)的特性正好契合。本文根据该特点, 将系统中的一个节点作为通信核, 完成任务的主控程序, 将系统中的其他多个节点作为计算核, 完成并行任务, 最终形成一个3层架构的高速并行处理模型。底层为传输层, 通过使用SRIO总线替代传统的以太网进行板间通信, 以提高传输效率, 降低通信延迟; 中间层为MPI接口层, 使用MPI协议进行并行处理, 以加快任务执行时间; 最上层为应用层, 执行具体的系统任务。其中MPI并行处理的框架如图 2所示。

|

| 图 2 嵌入式并行处理流程 |

MPI应用程序的任务执行原理是PPE(power processor element)上主程序对任务线程进行控制管理, 任务计算核心在SPE(synergistic processor element)端完成, 并且通过直接内存访问(DMA)操作与内存进行数据及结果的传输。而对于多节点MPI, 需要在单节点的基础上加上消息传递机制。

针对传统MPI运行效率方面的问题, 本文充分利用处理器中多个SPE, 使MPI任务线程可以占用不同SPE执行, 从而达到加速计算的目的, 仅需少量修改核心程序, 将其移植到SPE上运行。由于MPI任务间的通信操作都发生在PPE和主存端, SPE主要进行计算, SPE上执行的计算核心通常都是对大量数据的算术运算处理, 不会有复杂的逻辑控制指令, 能较好地发挥SPE的运算性能, 缩短程序的运行时间。通过上述模型可知, 确保系统实时性的前提, 是高速通信和高效计算。

2 通信模式设计点到点通信是MPI通信的基础, 集合通信是对点到点通信的扩展[7]。因此, 本文在设计MPI处理函数时, 主要划分为了点到点和集合通信两类。

2.1 点对点通信MPI点对点通信本质上是各子任务进程间的消息一对一传递, 而进程间通信最佳方案是共享内存(share memory)。通过在内存中申请部分空间作为消息缓冲区, 快捷地实现进程间的消息传递[8]。

缓冲区采用二维表进行设计, 即为每一对通信进程(ti, tj)都申请一块共享的消息缓冲区buffij, 则N个任务进程间相互通信时, 需要申请N2块缓冲区。ti和tj都可以对这块缓冲区进行读写, 实现进程间的通信。该设计方案的优点在于进程间相互独立, 不会出现缓冲区资源进程的情况, 避免死锁。

默认情况下, 对buffij申请使用时都是整块区域进行的, 该方式操作简单, 易于实现, 但缓冲区的使用效率会大大降低, 因为每次进行消息读写时都必须等待上一次消息读写完成后才能进行。所以, 在实际的应用中, 需要对buffij进行区域划分, 形成一个缓冲区队列, 这样能确保通信时只占用缓冲区的部分区域, 并在占用时可以进行反复的发送和接收操作, 直至完成通信并释放缓冲区。该方法能有效提高缓冲区的使用率, 提高并行效率, 唯一的缺点是需要额外的缓冲区管理程序开销。

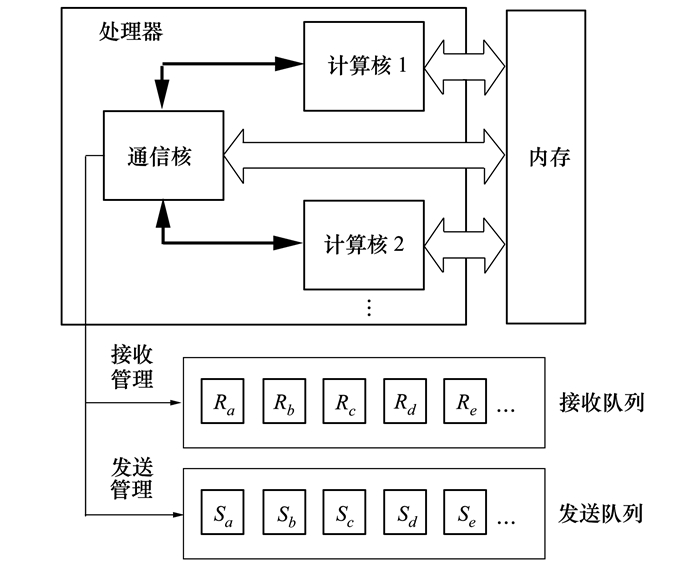

假设(ti, tj)已经申请了缓冲区块buff′ij, 为了防止ti和tj同时对buff′ij进行访问, 形成读写冲突, 可以参考PV操作实现对缓冲区的访问控制, 其设计方案如图 3所示。同时将接收队列和发送队列的分离, 形成双队列模式, 可以确保接收和发送操作互不干扰, 提高通信效率。

|

| 图 3 缓冲区操作流程 |

节点内通信时, 发送和接收都在同一内存中完成, 因此消息的传输实质是内存不同地址段的复制; 节点间通信时, 发送和接收方分别处于2个处理器(核), 通信双方需要通过存储器的缓冲区来存放总线需要收/发的消息。两者本质上都采用了共享内存的方式进行消息管理, 提高了任务调度的可操作性。

2.2 集合通信集合通信是MPI通信的基本功能, 其技术基础是点到点的通信。本文主要实现了基于MPI的广播(broadcast)、规约(gather)等集合通信功能。例如, 广播功能采用存储转发的方式实现, 即节点A上的进程T11进行广播时, 首先将其发送给节点B的进程T21, 之后分别由T11和T21将消息转发给同节点的其他进程。采用该方式, 可以有效地降低节点间的通信延迟, 提高传输效率。

3 测试与分析本实验在4块freescale生产的MPC8640D构成的小型并行系统上进行实验测试。该芯片具有2个e600内核, 每个内核的处理性能为1.5GHz。每个内核具有32kB的一级指令cache和数据cache, 以及一个1MB的二级cache。同时, MPC8641D还集成了一个用于通信的SRIO接口, 工作在4x模式下。每个芯片上运行VxWorks 5.5操作系统。

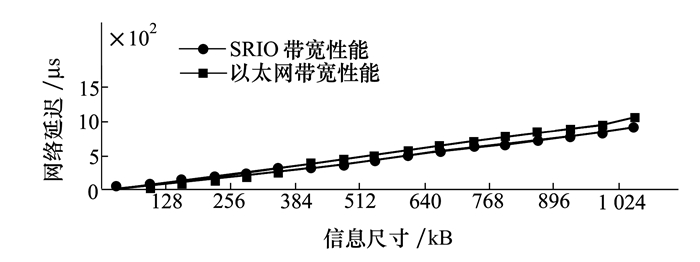

3.1 通信性能测试论文在对延迟和带宽等通信性能测试中使用了Ohio大学公布的MPI性能评估标准测试程序(下文简称OMT)进行测试。本实验在2种环境下进行测试, 一种是通过传输速率为1 000 Mbit/s以太网来对MPI进行实现的通信网络测试; 另一种是本文所构建的HPEPPM, 其SRIO硬件接口速率为1.25 Gbit/s。通过对2种测试程序结果的比对, 来验证模型的性能优劣。

方案1 通过OMT的测试程序中短消息和长消息的交替传输, 测试网络延迟。程序通过调用消息发送函数MPI-Send()和消息接收函数MPI-Recv()进行短消息和长消息交替传输, 计算网络平均延迟时间。具体测试结果如图 4所示。

|

| 图 4 延迟性能比较 |

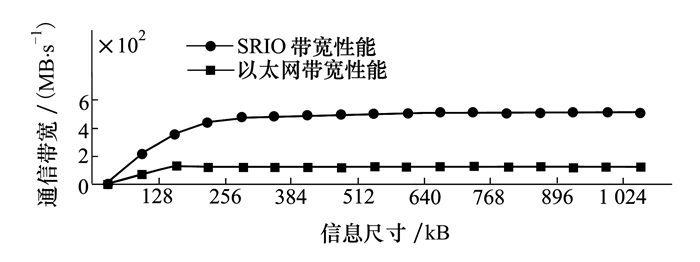

方案2 通过OMT的测试程序中定长消息的多次往返传输, 测试通信带宽。程序通过消息发送函数MPI-Send()和消息接收函数MPI-Recv()进行多节点的定长消息传输, 根据总时间和循环次数计算通信带宽。具体测试结果如图 5所示。

|

| 图 5 带宽性能比较 |

通过对比实验可以发现, 网络数据量较小时, HPEPPM与传统以太网的传输性能差距不大, 但当数据量逐渐增大时, HPEPPM与以太网的传输性能差距不断增加, 具体结论如下:

1) 网络延迟方面, SRIO网络表现出了较明显的优势。当数据量较小时, 两者延迟差不明显。当数据量较大时, 由于基于TCP/IP协议的通信带来的阻塞问题, 使得延迟增长较快。

2) 通信带宽方面, 两者差距非常明显。尤其是当通信量超过704 kB时, 其传输带宽为504 MB/s, 稳定在以太网传输带宽的5倍左右。由于SRIO使用8B/10B编码和包交换的相关协议字段开销, 导致测试结果与理论带宽存在差距。由于以太网在数据传输时, 存在流量控制, 防止接收端缓冲区消息被多次覆盖, 导致其传输带宽在128 kB时就已达到峰值121 MB/s, 且之后有所下降, 并稳定在105 MB/s; 而SRIO采用多流传输方式, 对大数据量的传输有优势。

3.2 数据处理性能测试论文在对数据处理性能测试上使用的测试程序为HPL(high performance linpack)。HPL是国际上通用的高性能平台测试方法, 目前TOP 500排名即是根据该测试程序的结果得到。HPL通过采用高斯消元法求解线性代数问题, 对处理平台的性能进行评估, 对于求解矩阵的规模为N的问题, 其计算量恒定为(2*N3)/3-2*N2, 因此通过对运行时间进行统计就可以得到Linpack峰值, 单位为GFLOPS。

使用HPL进行测试, 首先需要确定配置参数, 通过优化配置参数可以使HPL得到最好的测试结果。本文所采用的处理器为MPC8640D, 共包括1MB的L2 cache, 每个CPU节点分配1GB内存, 因此确定矩阵规模N为10 363, 矩阵分块大小为192。本文所使用的实验环境中共包括4片处理器, 每个处理器中一个核心负责计算任务, 一个核心负责通信任务, 因此属于节点数较多, 每个节点内CPU数较少的情况, 处理器阵列采用按列排布的方式, 并确定处理器网络P、Q分别为1、4。

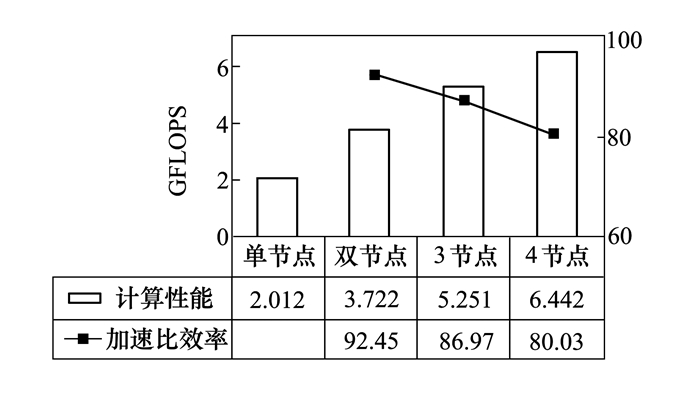

采用上述参数, 分别在不同数量节点情况下进行测试, 得到结果如图 6所示。

|

| 图 6 矩阵不变情况下不同节点计算性能对比图 |

通过上述测试结果可以发现, 在保持问题规模不变的前提下, 增加测试节点数量, 测试结果随之提高, 表明本文提出的并行处理模型具有良好的加速效果。在双节点情况下, 加速比效率最高, 达到92.45%。可见加速比效率并没有与节点数成正比, 造成该现象的原因是测试节点增加的同时也会导致节点间通信量增加, 因此加速比效率也随之下降。

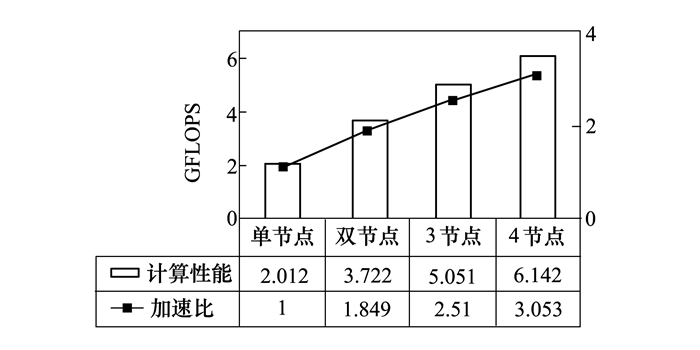

为了验证模型的可扩展性, 实验在保持其他参数不变的情况下, 同时线性增加节点数量和矩阵规模, 通过计算得到测试结果如图 7所示。

|

| 图 7 矩阵数随节点规模正比增长情况下的节点计算性能对比图 |

当前测试环境中可用节点数为4, 因此最大可实现4个MPI进程同时进行HPL测试。通过上述测试结果可以发现, 计算性能随着计算节点数增加而提高, 且加速比基本呈线性, 表明本文提出的并行处理模型具有良好的可扩展性。

4 结论本文在4片MPC8640D处理器通过SRIO总线进行互联的环境中, 分别对节点间的MPI通信带宽与通信延迟进行了测试。测试结果表明, 本文所提出的轻量级MPI实现方法通信开销小、速率高, 适用于资源受限的嵌入式系统。另一方面, 本文采用计算任务与通信任务并行执行的方法, 保证了此2种任务能相互独立执行, 同时提高了计算效率与通信效率。

| [1] | Muraoka D, Yasugi M, Hiraishi T, et al. Evaluation of an MPI-Based Implementation of the Tascell Task-Parallel Language on Massively Parallel Systems[C]//International Conference on Parallel Processing Workshops, 2016:161-170 |

| [2] | Si M, A, A J, Balaji P, et al. MT-MPI:Multithreaded MPI for Many-Core Environments[C]//ACM International Conference on Supercomputing, 2014:125-134 |

| [3] | Wu X, Taylor V. Performance Characteristics of Hybrid MPI/OpenMP Scientific Applications on a Large-Scale Multithreaded BlueGene/Q Supercomputer[C]//ACIS International Conference on Software Engineering, Artificial Intelligence, 2013:303-309 |

| [4] | Aubrey-Jones T, Fischer B. Synthesizing MPI Implementations from Functional Data-Parallel Programs[J]. International Journal of Parallel Programming, 2016, 44(3): 1-22. |

| [5] | Matveeva N, Suvorova E, Sheynin Y. QoS Mechanisms in Space Fibre and RapidIO:SpaceWire Networks and Protocols, Long Paper[C]//International SpaceWire Conference, 2016 |

| [6] | Baymani S, Alexopoulos K, Valat S. Exploring RapidIO Technology within a DAQ System Event Building Network[C]//IEEE-NPSS Real Time Conference, 2016:1-4 |

| [7] | Klilou A, Belkouch S, Elmaizi A, et al. Case Studies of Data Traffic Management on a High-Performance Computing System Based on Multi-DSPs and Serial RapidIO Interconnect[C]//IEEE International Conference on Information Technology for Organizations Development, 2016:1-6 |

| [8] | Shu L, Hao J, Song Y, et al. Optimal Many-to-Many Personalized Concurrent Communication in RapidIO-Based Fat-Trees[C]//IEEE/ACIS International Conference on Software Engineering, Artificial Intelligence, Networking and Parallel/Distributed Computing, 2016:343-350 |

| [9] | Goodwin S A, Weed R A, Sankar L N, et al. Toward Cost-Effective Aero-elastic Analysis on Advanced Parallel Computing Systems[J]. Journal of Aircraft, 2015, 36(36): 710-715. |

| [10] | Prokopec A. Data Structures and Algorithms for Data-Parallel Computing in a Managed Runtime[D]. Switzerland, Ecole Polytechnique Fédérale de Lausanne, 2014 |

2. School of Software and Microelectronics of Northwestern Polytechnical University, Northwestern Polytechnical University, Xi'an 710072, China